Second Edition

# Electronics and Communications for Scientists and Engineers

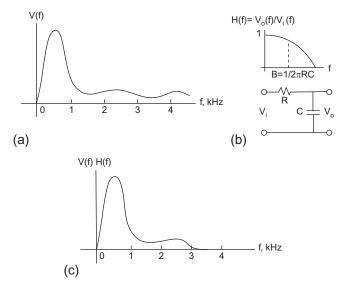

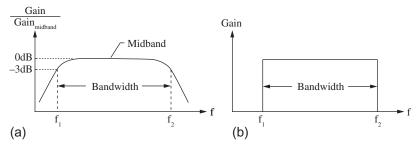

Martin Plonus

# Electronics and Communications for Scientists and Engineers

# Electronics and Communications for Scientists and Engineers

Second Edition

Martin Plonus

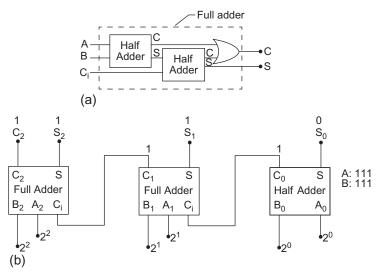

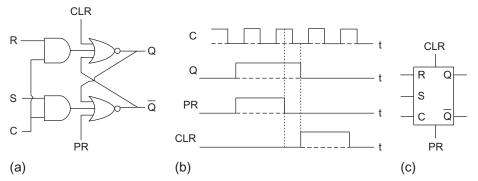

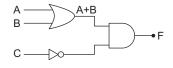

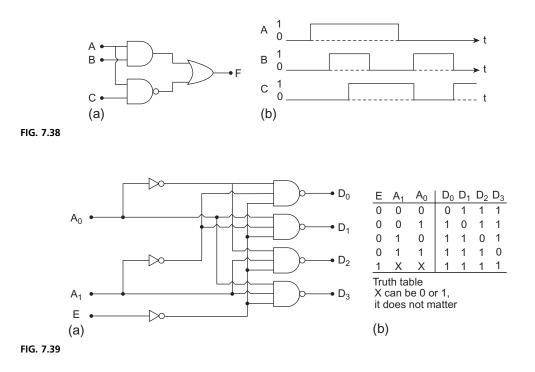

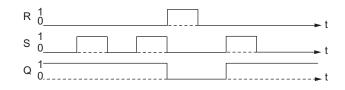

Butterworth-Heinemann An imprint of Elsevier

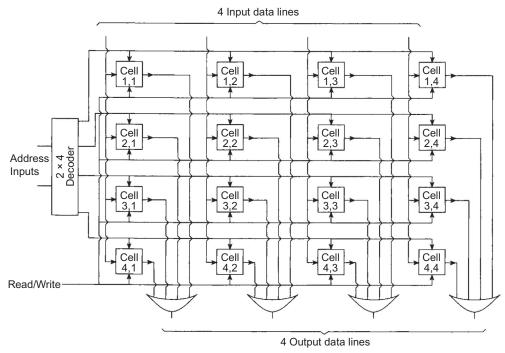

Butterworth-Heinemann is an imprint of Elsevier The Boulevard, Langford Lane, Kidlington, Oxford OX5 1GB, United Kingdom 50 Hampshire Street, 5th Floor, Cambridge, MA 02139, United States

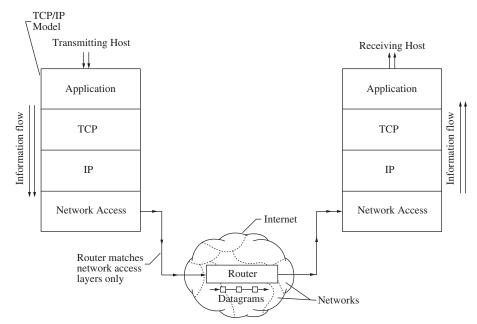

© 2020 Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher. Details on how to seek permission, further information about the Publisher's permissions policies and our arrangements with organizations such as the Copyright Clearance Center and the Copyright Licensing Agency, can be found at our website: www.elsevier.com/permissions.

This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods, professional practices, or medical treatment may become necessary.

Practitioners and researchers must always rely on their own experience and knowledge in evaluating and using any information, methods, compounds, or experiments described herein. In using such information or methods they should be mindful of their own safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors, assume any liability for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the material herein.

#### Library of Congress Cataloging-in-Publication Data

A catalog record for this book is available from the Library of Congress

#### British Library Cataloguing-in-Publication Data

A catalogue record for this book is available from the British Library

ISBN: 978-0-12-817008-3

For information on all Butterworth-Heinemann publications visit our website at https://www.elsevier.com/books-and-journals

Publisher: Katey Birtcher Editorial Project Manager: Susan Ikeda Acquisition Editor: Katey Birtcher Production Project Manager: James Selvam Cover Designer: Christian J. Bilbow

Typeset by SPi Global, India

to grow libraries in

www.elsevier.com • www.bookaid.org

# Preface

# Focus of the book

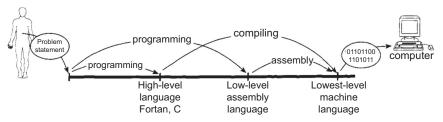

Although the audience for this book is the same as that for broad-based electrical engineering texts, this book differs in length, structure, and emphasis. Whereas the traditional texts for nonelectrical engineering cover circuits and electronics and then treat electrical machinery, we believe that it is more important for today's students to be knowledgeable in digital technology than in electrical machinery. After developing circuits and analog electronics in the early chapters of this text, we continue with digital electronics and conclude with chapters on the digital computer and on digital communications—chapters that are normally not included in books for non-EEs.

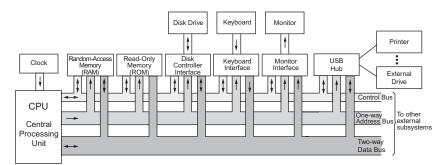

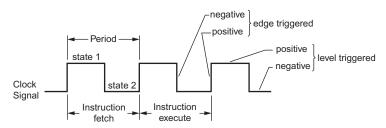

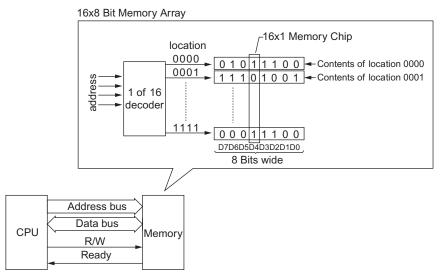

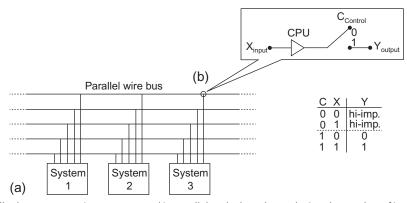

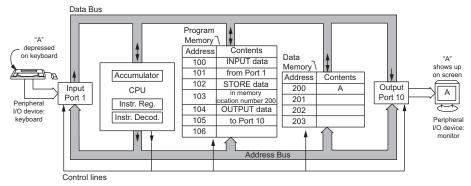

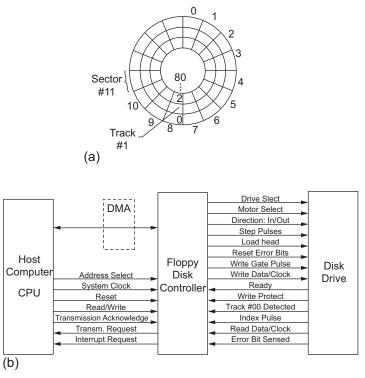

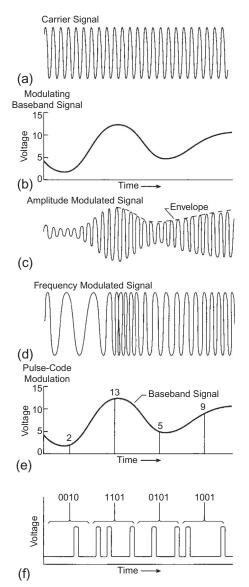

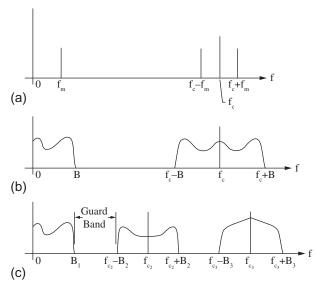

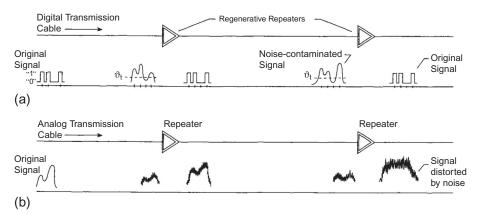

The text is intended for students who need to understand modern electronics and communication. Much of the material in the book is developed from the first principles, so previous courses on circuits, for example, are not required; only freshman math and physics courses, and the elementary treatment of circuits that freshman physics provides, are expected. The emphasis throughout the book is on applications and on understanding the underlying principles. For example, Chapter 8 is presented from the perspective of a user who needs to understand the various subsystems of a computer, including the relationship of hardware and software such as operating systems and application programs. Expertise in designing computers is thus left to more advanced courses. Similarly, Chapter 9 on digital communication is sufficiently detailed to present the information sampling and pulse code modulation necessary for an understanding of such diverse subjects as digital signal processing, the audio CD, and the Internet. More advanced topics are left to specialized communication texts.

Presenting and teaching circuits, electronics, and digital communications from a single textbook can be an advantage if nonmajors are limited to a single EE course, which seems to be the trend at many schools.

## Motivation for the book

Electrical engineering began in the power industry, rapidly progressed to electronics and communications, and then entered the computer age in the 1960s. Today, electrical and electronic devices, analog and digital, form the backbone of such diverse fields as computer engineering, biomedical engineering, and optical engineering, as well as financial

markets and the Internet. For example, the electronics in a modern aircraft constitute about 50% of the total cost.

This text is an outgrowth of lecture notes for a one-term course titled Applications of Electronic Devices that is offered, on an elective basis, to non-electrical-engineering students. It provides a sufficiently deep understanding of this subject for students to interact intelligently with other engineers. The goal is not so much to teach design as to present basic material in sufficient depth so that students can appreciate and understand the application chapters on operational amplifiers, the digital computer, and digital communication networks. A suitable textbook for such a course did not exist. Typical electronics texts omit circuits and communications and are too detailed. On the other hand, texts on electrical engineering for non-EEs are very broad, with material on machinery and power engineering that is not relevant to electronics and communication. In addition, the breadth of these texts, when used in a one-term course, often forces the omission of certain sections, making the flow of the presentation choppy. Finally, encyclopedic books that are useful as references for designing circuits are much too advanced for nonmajors. What is needed is a text brief enough for a one-term course that begins with chapters on AC and DC circuits, then progresses to analog and digital electronics, and concludes with application chapters on contemporary subjects such as digital computers and digital communication networks-demonstrating the importance as well as the underlying basis of electronics in modern technology. These views were used as guidelines for writing this text.

# Organization of the book

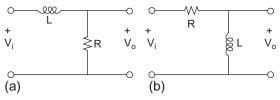

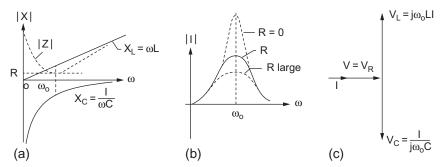

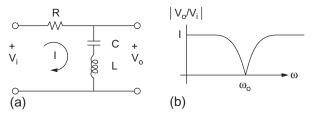

The book has three basic parts: circuits, electronics, and communications. Because electronics is basically the combination of circuit elements *R*, *L*, and *C* and active elements such as a transistor, we begin the book with a study of circuits. DC circuits are presented first because they are simpler but still permit the development of general principles such as Thevenin's theorem, maximum power transfer, and "matching." Resistors, defined by Ohm's law, are shown to be energy conversion elements, and capacitors and inductors are energy storage elements. The distinction between ideal and practical sources is stressed before loop equations are introduced as a method for solving for currents and voltages anywhere in a circuit. AC circuits are considered in Chapter 2, where we first learn that in a circuit, currents and voltages can change significantly with changes in the frequency of the applied source. Resonance, band-pass action, and bandwidth are a consequence. Average power, effective values of AC or of any periodic waveform, transformers, and impedance matching complete the chapter. These two chapters provide the basic understanding of DC and AC circuits, of transient analyses, and of frequency response and in that sense serve as a foundation for the remainder of the book.

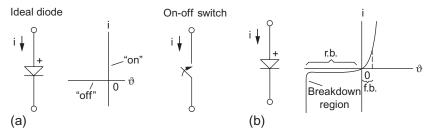

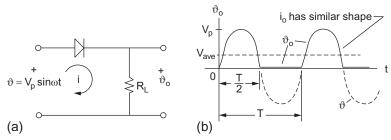

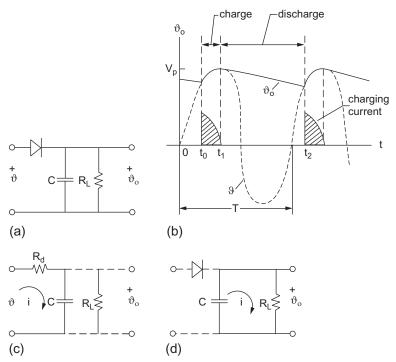

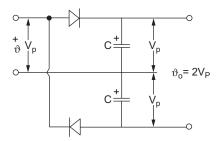

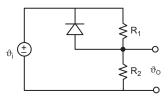

In Chapter 3 we add a new element, a diode, to a circuit. Omitting lengthy theory, we simply define a diode as a fast on–off switch which in combination with *RLC* elements

makes possible clippers, clampers, voltage regulators, SCRs, etc. However, we emphasize its use in power supplies that change AC to DC. As DC powers most electronic equipment, a power supply is an important component in computers, TVs, etc. A simple power supply consisting of a rectifier and capacitor filter is designed. This simple design nevertheless gives the student an appreciation of the concept, even though modern power supplies can be quite complicated circuits.

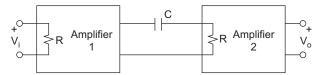

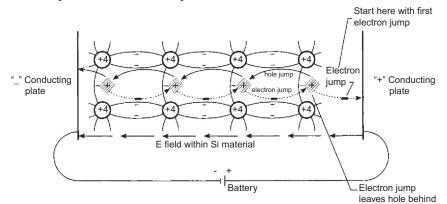

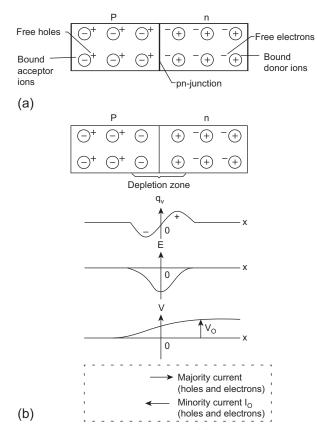

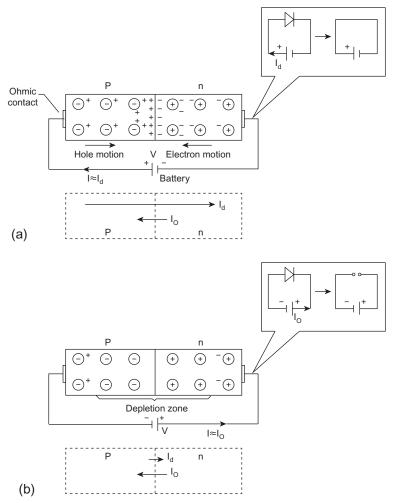

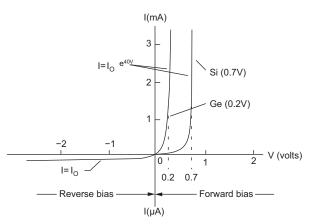

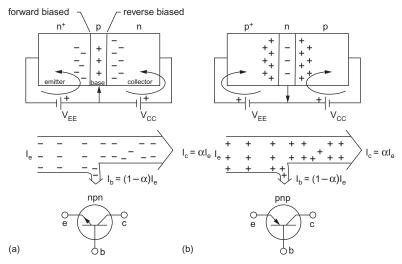

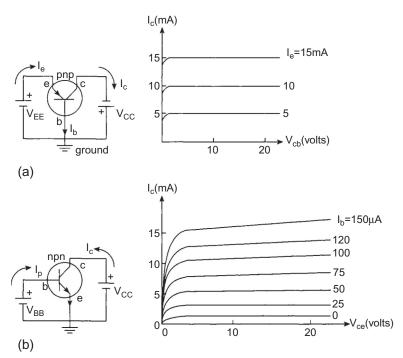

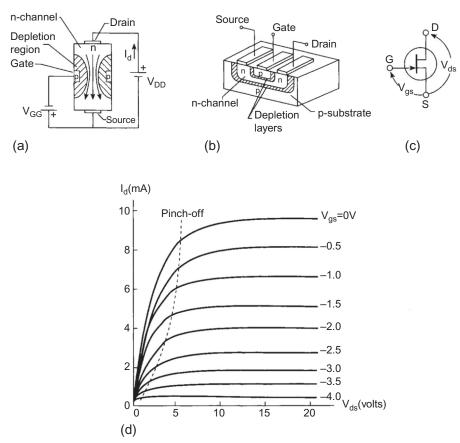

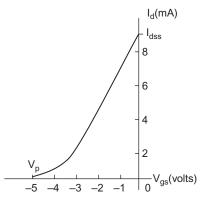

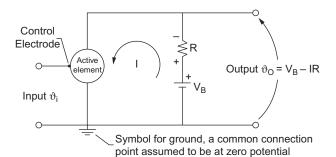

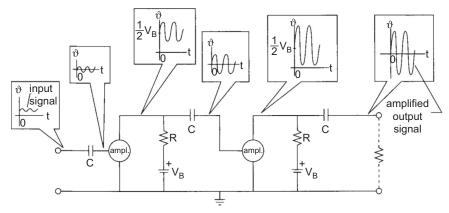

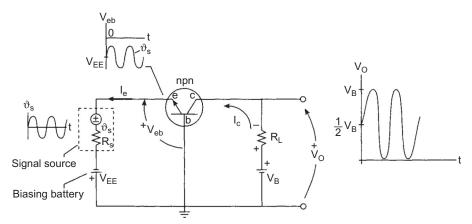

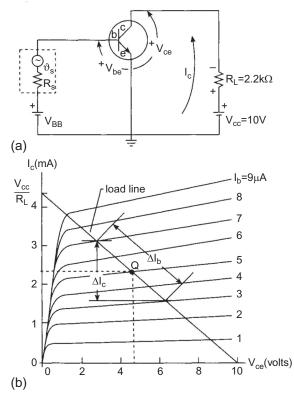

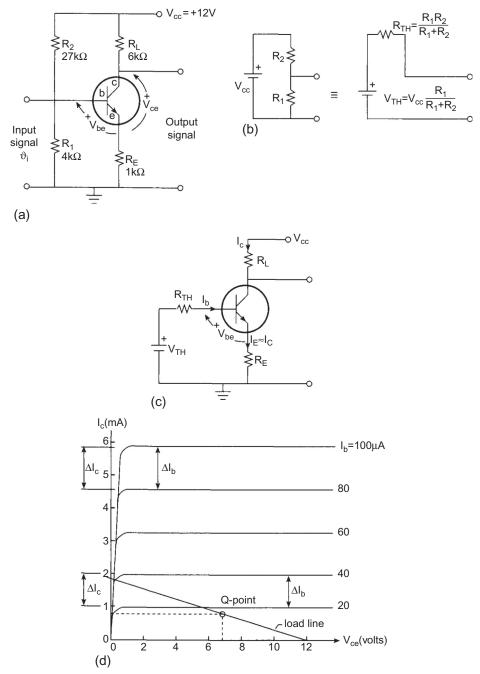

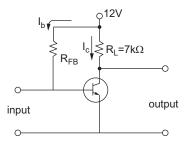

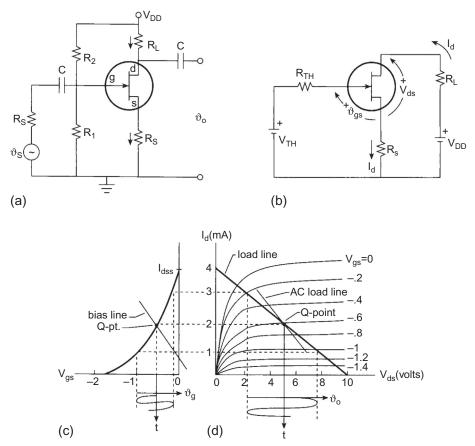

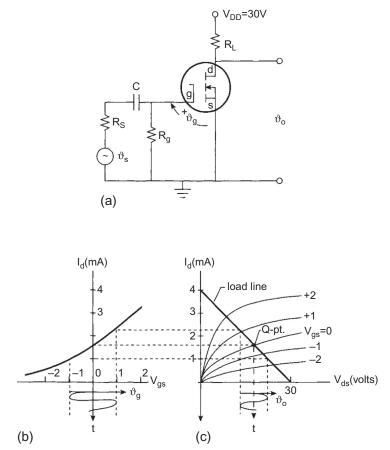

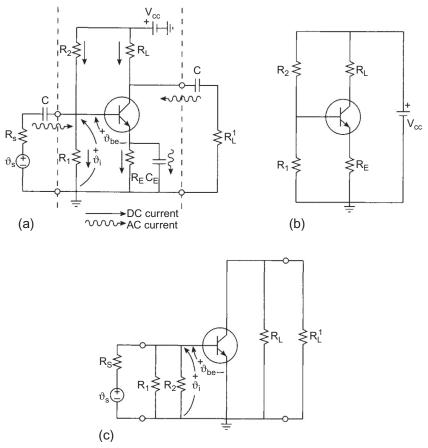

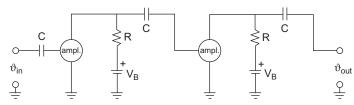

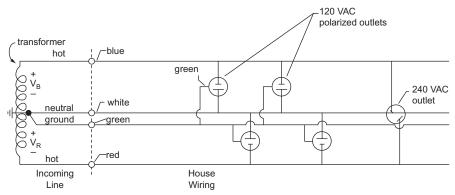

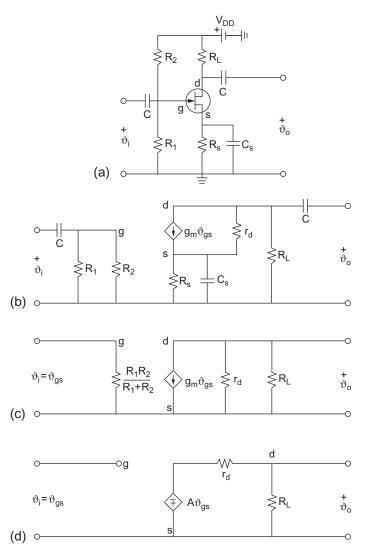

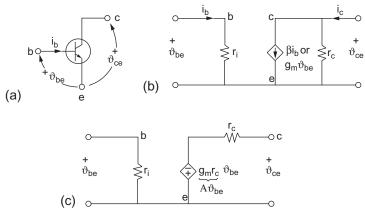

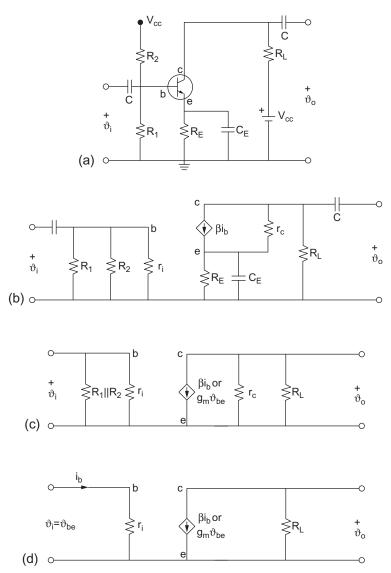

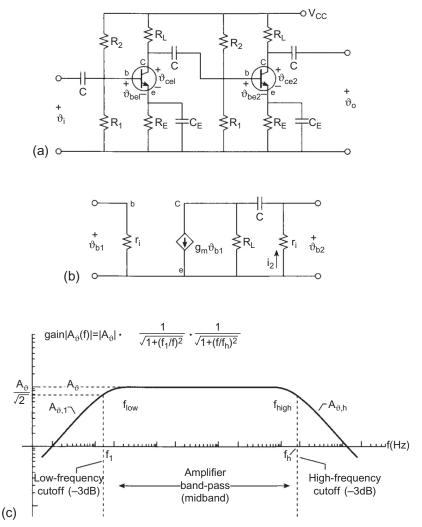

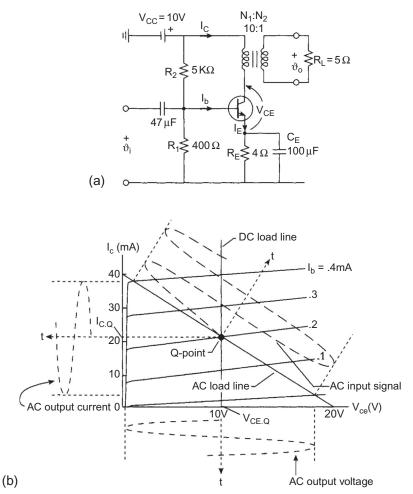

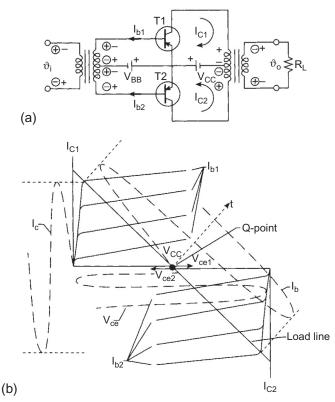

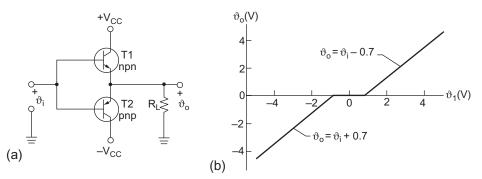

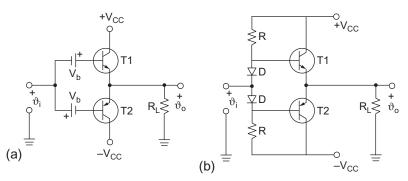

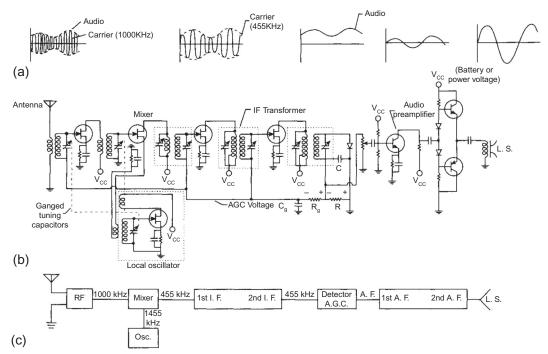

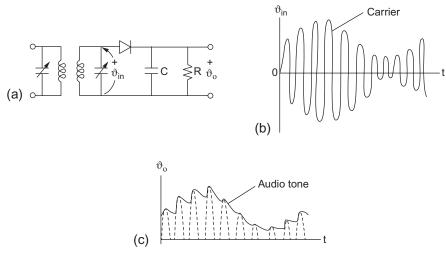

In Chapter 4 we begin the study of electronics with the underlying physics of the *pn* junction, which can explain diode and transistor action for students who are baffled by these seemingly mystical devices. Equally baffling is the transistor's ability to amplify, which we approach by first considering a graphical analysis of an amplifier circuit. The notion of a load line imposed by the external circuit to a transistor and drawn on the transistor characteristic graphs seems to be acceptable to the student and is then easily extended to explain amplifier action. The load line and *Q*-point also help to explain DC biasing, which is needed for proper operation of an amplifier. Only then is the student comfortable with the mathematical models for small-signal amplifiers. After frequency response, square wave testing, and power amplifiers, we are ready to consider a complete system. As an example we dissect an AM radio receiver and see how the parts serve the system as a whole, noting that the electronics of most AM receivers these days come as integrated chips allowing no division into parts. Chapters 3, 4, and 5 cover analog electronics, and large parts of these chapters could be omitted if the choice is made to deemphasize analog and devote more class time to digital electronics.

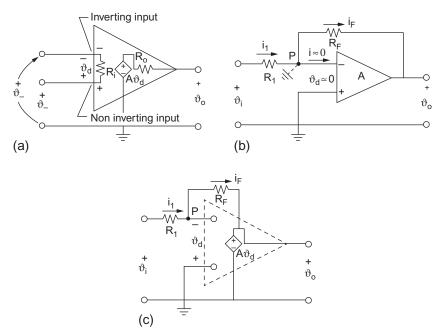

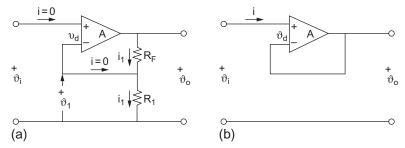

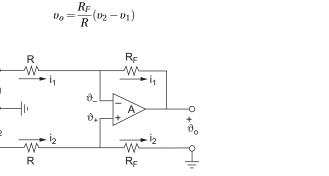

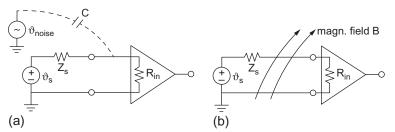

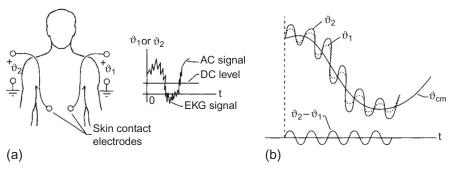

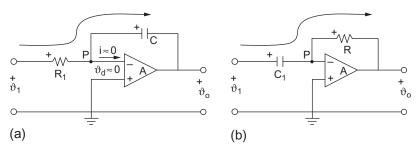

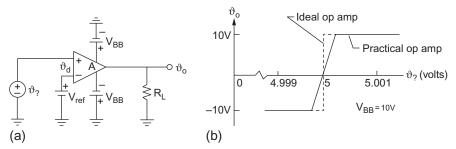

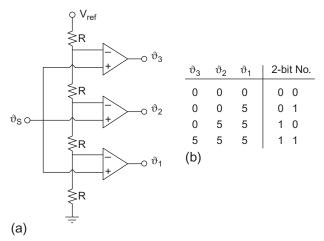

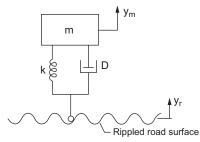

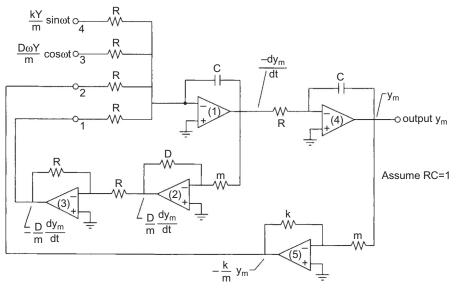

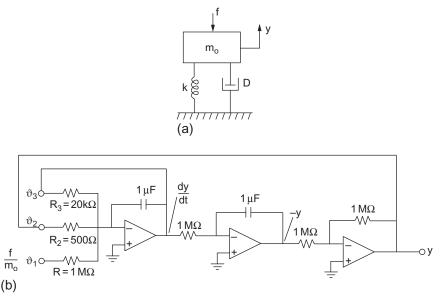

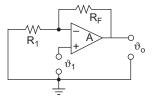

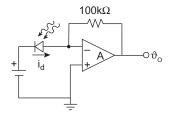

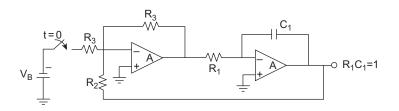

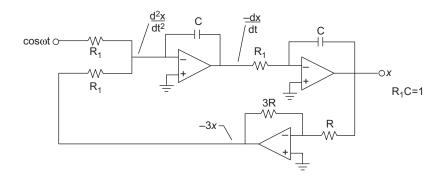

Operational amplifiers are the subject of Chapter 6. This chapter can stand alone because it is to a large extent independent of the previous three chapters on analog electronics. After presenting the standard inverting op amp circuit, which is characterized by moderate but stable gain obtained by applying large amounts of negative feedback to the op amp, we consider a wide variety of practical op amp devices from summers, comparators, integrators, differential amplifiers, filters, A/D, and D/A converters. A final example of the analog computer is given primarily because it applies to control, teaches us a tad more about differential equations, and shows how a mechanical system can be effectively modeled and solved by electrical circuits.

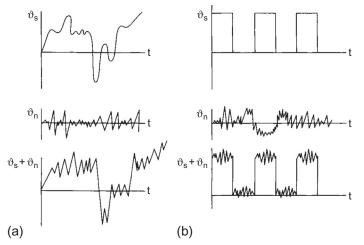

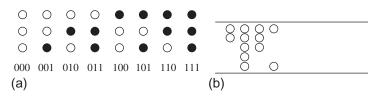

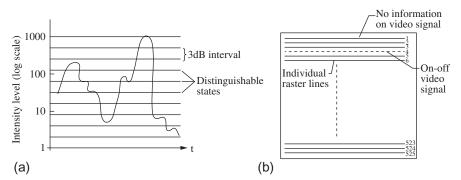

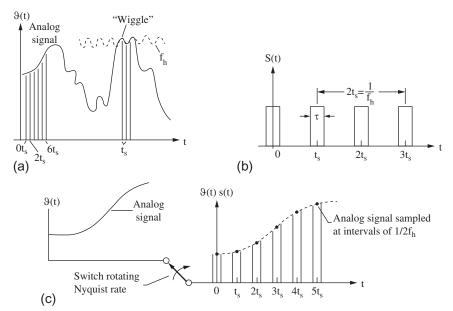

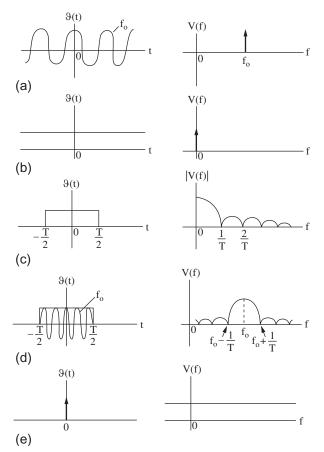

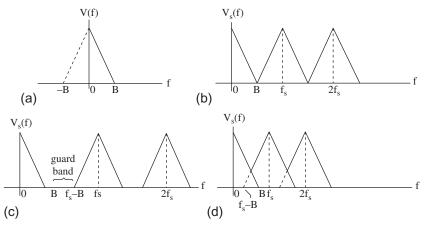

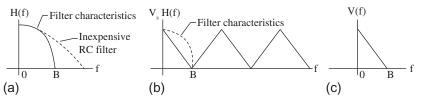

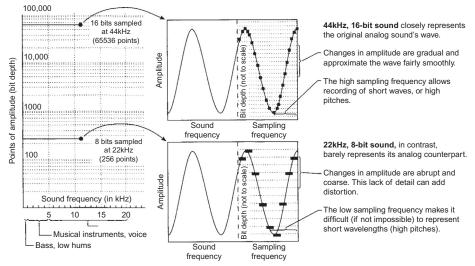

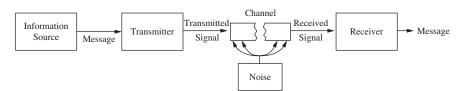

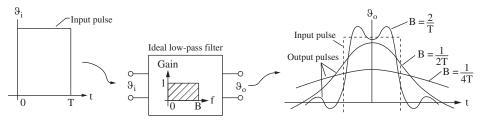

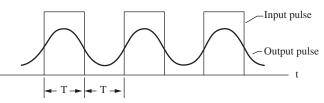

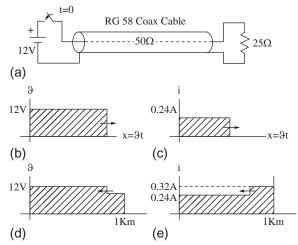

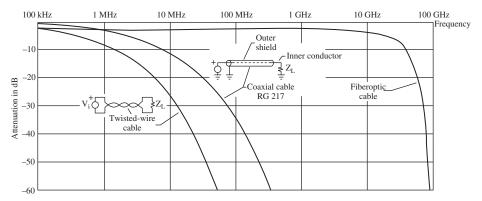

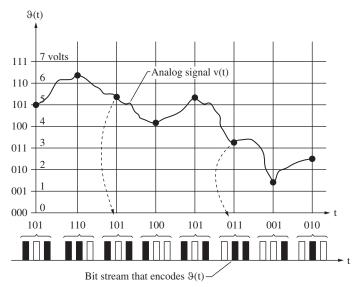

The final three chapters consider the subject of digital electronics. The last chapter, even though on digital communication, is nonetheless rooted in electronics. Our objective for these chapters is to give the student a deeper understanding of the digital computer and the Internet, cornerstones of the digital revolution. Gates, combinatorial and sequential logic, flip-flops, and the microprocessor (Experiment 9), all building blocks for more complex systems, are considered in Chapter 7. We move to the digital computer in Chapter 8 and to communication networks in Chapter 9. These chapters are not so much intended to teach design skills as they are for the nonmajor to acquire a thorough understanding of the subject matter for a workable interaction with experts. In that sense, the chapter on the digital computer concentrates on those topics with which the user interacts such as programming languages, RAM and ROM memory, the CPU, and the operating system. Similarly, in Chapter 9 we cover the sampling process, Nyquist criterion, information

rates, multiplexing, and pulse code modulation, all of which are necessary for an understanding of digital signal processing and digital communication networks such as the Internet.

# Acknowledgments

# First edition

I thank Dr. Carl J. Baumgaertner of Harvey Mudd College, Dr. Shawn Blanton of Carnegie Mellon University, Dr. Gary Erickson of Idaho State University, and Dr. Can E. Korman of The George Washington University for reviewing the manuscript. I also thank my colleagues at Northwestern University, Professors Larry Henschen, Mike Honig, Zeno Rekasius, and Alan Sahakian, for reviewing portions of the manuscript.

# Second edition

I would like to thank Professor Larry Henschen for help in updating Chapter 8 (The Digital Computer), Professor Randall Berry for contributing primarily to the "Compression" section, Professors Douglas Downey and Selim Shahriar for contributing primarily to the "Artificial Intelligence" and "Quantum Computer" sections, respectively, in Chapter 9, Professor Gordon J. Murphy for critically reviewing many sections, and students Jing Li and Julian Gamboa for help with graphs and proofreading.

Martin Plonus

# 1

# **Circuit Fundamentals**

# 1.1 Introduction

Electronics deals with voltage and current interaction in a network of resistances R, inductances L, capacitances C, and active elements such as transistors. The purpose is usually to amplify signals or to produce signals of a desired waveform, typically at low levels of power. A study of electronics therefore should begin with the passive elements R, L, and C—a study usually referred to as *circuit theory*.

It should then be followed by the basics of transistors, which generally act as amplifiers or on–off switches. We can then proceed to electronic circuit design in which passive and active elements are combined to form elementary circuits such as a power supply, amplifier, oscillator, A/D converter, etc. In turn we can combine these elementary circuits to create useful devices such as radios, TVs, computers, etc.

The study of electronic circuits will essentially follow this path: DC circuit analysis, AC circuit analysis, basic solid-state theory, junction diodes, transistors, elementary amplifiers and op amps, small-signal amplifier circuits, and digital electronics, which are then used as building blocks to introduce digital communications and the Internet.

# 1.2 Dimensions and Units

In this book the mksa (meter-kilogram-second-ampere) system of units, now a subsystem of the SI units, is used. A dimensional analysis should always be the first step in checking the correctness of an equation.<sup>1</sup> A surprising number of errors can be detected at an early stage simply by checking that both sides of an equation balance dimensionally in terms of the four basic dimensions. For example, Newton's second law gives the force *F* in newtons (N) as

$F = ma \text{ mass}(\text{length})/(\text{time})^2$

An increment of work dW in *joules* (J) is given by

$dW = F dl \operatorname{mass}(\operatorname{length})^2 / (\operatorname{time})^2$

<sup>1</sup>A *dimension* defines a physical characteristic. A *unit* is a standard by which the dimension is expressed numerically. For example, a second is a unit in terms of which the dimension time is expressed. One should not confuse the name of a physical quantity with its units of measure. For example, power should not be expressed as work per second, but as work per unit time.

#### 2 Electronics and communications for scientists and engineers

where dl is an incremental distance in *meters* (m). *Power*<sup>2</sup> in *watts* (W), which is the time rate of doing work in joules per second, is

$$P = \frac{dW}{dt} \operatorname{mass}(\operatorname{length})^2 / (\operatorname{time})^3$$

The next quantity that we want to consider is the electric current, I = dQ/dt, measured in *amperes* (A), which is the rate of flow of electric charge Q, measured in *coulombs* (C). The smallest naturally occurring charge e is that possessed by an electron and is equal to  $-1.6 \cdot 10^{-19}$  C. A coulomb, which is a rather large charge, can be defined as the charge on  $6.28 \cdot 10^{18}$  electrons, or as the charge transferred by a current of 1 A in 1 s. Any charged object is a collection of elementary particles, usually electrons. The possible values of total charge Q of such an object are given by

$Q = \pm ne$  where n = 0, 1, 2, ...

Electric charge is quantized and appears in positive and negative integral multiples of the charge of the electron. The discreteness of electric charge is not evident simply because most charged objects have a charge that is much larger than *e*.

### 1.3 Basic Concepts

#### 1.3.1 Electric Field

Coulomb's law states that a force *F* exists between two charges  $Q_1$  and  $Q_2$ . This force is given by  $F = kQ_1Q_2/r^2$ , where *k* is a proportionality constant and *r* is the distance between the charges. Hence each charge is in a force field<sup>3</sup> of the other one as each charge is visualized as producing a force field about itself. We can now define an *electric field E* as a force field per unit charge.

$$E = \frac{F}{Q} \tag{1.1}$$

For example, the electric field which acts on charge  $Q_1$  can be stated as  $E = F/Q_1 = k \cdot Q_2/r^2$ . Hence for those that are more comfortable with mechanical concepts, one can think of an electric field as a force that acts on a charge.

#### 1.3.2 Voltage

Voltage, or *potential difference*, can be introduced similarly by considering work. If we view a small amount of work as a small motion in a force field, and replace the force by  $F = Q \cdot E$ ,

<sup>&</sup>lt;sup>2</sup>Note that in this book we also use W as the symbol for energy. This should not lead to any confusion as it should be self-evident which meaning is intended.

<sup>&</sup>lt;sup>3</sup>There are various force fields. For example, if force acts on a *mass* it is referred to as a gravitational field, if it acts on an *electric charge* it is an electric field, and if it acts on a *current-carrying* wire it is a magnetic field.

we obtain  $dW = Q \cdot E \cdot dl$ . We can now define a *voltage*, measured in *volts* (V), as work per unit charge, i.e.,

$$dV = \frac{dW}{Q} = E \cdot dl \tag{1.2}$$

Hence a small voltage corresponds to a small displacement of a charge in an electric force field.

It is useful to consider the inverse operation of Eq. (1.2), which expresses work as an integration in a force field, that is,  $V = \int E dl$ . The inverse operation gives the force as the gradient of the work, or

$$E = -\frac{dV}{dl}$$

in volts/meter (V/m) (1.3)

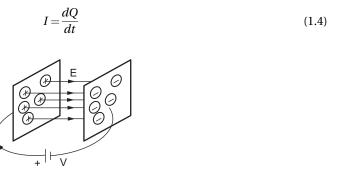

For example, to create a fairly uniform electric field one can connect, say, a 12 V battery to two parallel metallic plates as shown in Fig. 1.1.

If the plates are separated by 10 cm, an electric field of E = 12 V/0.1 m = 120 V/m is created inside the space. If an electron were placed inside that space, it would experience a force of

$$1.6\cdot 10^{-19}\cdot 120 = 1.9\cdot 10^{-17}\cdot N$$

and would begin to move toward the positive plate. As another example of the usefulness of the gradient expression for the electric field (Eq. 1.3), let us consider a receiving antenna which is in the field of a radio transmitter that radiates an electric field. If the electric field at the receiving antenna is 1 mV/m, then a 1-m-long antenna would develop a voltage of 1 mV. If a transmission line connects the antenna to a radio receiver, this voltage would then be available to the receiver for amplification.

#### 1.3.3 Current

Current, measured in amperes (A), is the time rate at which charges *Q* pass a given reference point (analogous to counting cars that go by a given point on the road and dividing by the time interval between counts). Thus

FIGURE 1.1 A uniform electric field E is created inside the space between two parallel plates.

As Benjamin Franklin assumed charge to be positive, the direction of current (ever since his day) is given by the direction that positive charges would flow when subjected to an electric field. Hence in Fig. 1.1 the current *I* that flows in the wire connecting the battery to the plates has the direction of positive charge flow. On the other hand we now know that current in a conducting wire is due to moving electrons which carry a negative charge. The direction of *I* and electron flow are therefore opposite. Similarly, if the space between the plates is occupied by positive charges, flow would be from the left to the right plate (the direction of *I*), but if occupied by electrons, flow would be from the right to the left plate.<sup>4</sup>

#### 1.3.4 Power

If we take the expression for power, which is the rate of doing work, and multiply it by dQ/dQ we obtain

$$P = \frac{dW}{dt} = \frac{dW}{dt}\frac{dQ}{dQ} = \frac{dW}{dQ}\frac{dQ}{dt} = VI$$

(1.5)

Hence *power is voltage multiplied by current*. When combined with Ohm's law, this is one of the most useful expressions in electronics.

#### 1.3.5 Ohm's Law

Thus far we have a picture of current as a flow of charges in response to an applied electric field. Current in a conducting medium though, such as copper or aluminum, is fundamentally different. A piece of copper is neutral, overall and at every point. So, if copper has no free charge, how does a copper wire conduct a current? A conducting medium such as copper is characterized by an atomic structure in which the atoms have only one, weakly attached electron in the outer shell. Hence, even a small force, such as a small electric field, created by a small voltage across the copper wire will make the electrons move. While such motion within the wire takes place—that is, a current flows in the wire—charge neutrality throughout the wire is always preserved (charge does not accumulate in the conductor). Hence, when a current flows in a segment of copper wire, the copper does not make any net electrons available—electrons simply leave one end of the segment while at the other end the same number enters.

There is now a subtle difference between electrons moving in vacuum and electrons moving in copper or in any solid conductor. It appears that electrons in both media are free in a sense, except that an electron in copper is free to move only until it collides with one of the many copper atoms that occupy the metal. It is then slowed down and must again be accelerated by the electric field until the next collision. Hence the progression

<sup>&</sup>lt;sup>4</sup>Note that a battery connected to two plates as shown in Fig. 1.1 produces a current only during a brief interval after connection. More on this when we consider capacitors. Current could also flow if the space between the plates is filled with free charges.

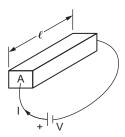

**FIGURE 1.2** A resistor is formed when a material of resistivity  $\rho$  is shaped into a bar of length  $\ell$  and cross-sectional area A.

of electrons in a conducting medium is one of colliding with many atoms while moving slowly through the metal. The current through such a material is therefore determined by the resistance to electron flow due to collisions and by the voltage across the material which provides the energy for successive accelerations after collisions. *Resistivity*  $\rho$  is a material property that relates to the average interval between collisions. Incorporating the geometry of a conductor, as shown in Fig. 1.2, the resistance *R* of a bar  $\ell$  meters long and *A* square-meters in cross-section is given by

$$R = \rho \frac{\ell}{A} \tag{1.6}$$

Hence the resistance increases with length but decreases with cross-sectional area. The unit of resistance is the *ohm*, denoted by the Greek letter  $\Omega$ . The reciprocal of resistance, called *conductance G*, is also used; the unit of conductance is the *siemens* (S). A typical value of resistivity for a good conductor such as copper is  $\rho = 1.7 \cdot 10^{-8}$  ohmmeters ( $\Omega$ -m), whereas for a good insulator such as glass it is  $10^{12} \Omega$ -m. This is a very large difference and implies that even though copper can carry large amounts of current, for all practical purposes the ability of glass to carry even tiny amounts of current is negligible.

A current in a conductor is maintained by placing a voltage across it. A larger voltage provides more energy for the electrons, and hence more current flows in the conductor. Resistance is the constant of proportionality between current and voltage, that is,

$$V = RI \tag{1.7}$$

This is a fundamental relationship and is known as *Ohm's law*. It states that *whenever a conductor carries a current, a voltage must exist across the conductor*. Figure 1.2 shows a simple circuit to which Eq. (1.7) applies. The connecting wires between the voltage source and the bar are assumed to have zero resistance. Hence the voltage *V* is directly applied to the bar resistor.

#### 1.3.6 Joule's Heating Law

During current flow in a metal, the repeated collisions of the electrons with the lattice atoms transfer energy to the atoms with the result that the temperature of the metal increases. A resistor can therefore be considered as an energy-transforming device: it converts electrical energy into heat. There are numerous everyday examples of this. An electric heater, a hair dryer, electric stove, etc., all contain resistors (usually tungsten wire) that give off heat when an electric current passes. The rate of energy conversion by a resistor can be expressed by substituting Eq. (1.7) in Eq. (1.5), which gives

$$P = VI = I^2 R = \frac{V^2}{R} \tag{1.8}$$

The expression  $P = I^2 R$  is known as *Joule's law* and *P* is power (equal to rate of change of energy) and is measured in *watts* (W). If we integrate this expression we obtain the thermal energy *W* dissipated in a resistor over a time interval *T*,

$$W = I^2 R T \tag{1.9}$$

where it was assumed that current and resistance remain constant over the time interval. This is known as *Joule's heating law*, where the units of *W* are in joules (J).

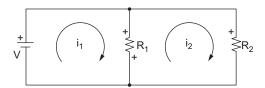

#### 1.3.7 Kirchhoff's Laws

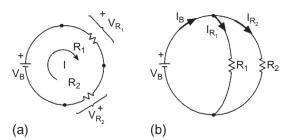

A circuit is an interconnection of *passive* (resistors, capacitors, inductors) and *active* (sources, transistors) elements. The elements are connected by wires or leads with negligible resistance. The circuit can be a simple one with one closed path, for example, a battery connected to a resistor (Fig. 1.2), or the circuit can be more elaborate with many closed paths. Figure 1.3a shows a simple, one-loop closed path circuit in which a battery forces a current to flow through two resistors (represented by "zig-zag" symbols) connected in series. We now observe, and we can state it as a rule, that current around the loop is continuous. That is, in each of the three, two-terminal elements the current entering one terminal is equal to the current leaving the other terminal at all times. In addition, the polarity convention can be used to differentiate between sources and sinks. For example, the current in the battery flows into the negative terminal and comes out at the positive terminal—this defines a source and voltage  $V_{\rm B}$  is called a *voltage rise*. Resistors, which absorb energy, are called *sinks*. In a sink, the current enters the positive terminal and the voltage across a sink is called a *voltage drop*.<sup>5</sup> It should now be intuitively obvious that in a circuit, voltage rises should equal voltage drops. Kirchhoff's voltage law states this precisely: the algebraic sum of the voltages around any closed path in a circuit is zero. Mathematically this is stated as

<sup>&</sup>lt;sup>5</sup>At times a battery can also be a sink. For example, connecting a 12 V battery to a 10 V battery (plus to plus and minus to minus) results in a one-loop circuit where current flows from the negative to positive terminal of the 12 V battery (a source), and flows from the positive to negative terminal of the 10 V battery (a sink). Of course what is happening here is that the 10 V battery is being charged by the 12 V battery.

FIGURE 1.3 (a) A battery is connected to two resistors in series. (b) A battery with two resistors in parallel.

$$\sum V_n = 0 \tag{1.10}$$

Applying Eq. (1.10) to the circuit of Fig. 1.3a, we obtain  $V_{\rm B} = V_{R_1} + V_{R_2}$ .

A *node* is defined as a point at which two or more elements have a common connection, as for example in Fig. 1.3b, where two resistors in parallel are connected to a battery to form a two-node, two-loop circuit. *Kirchhoff's current law* states that at a node, the algebraic sum of the currents entering any node is zero. Mathematically this is stated as

$$\sum I_n = 0 \tag{1.11}$$

Applying Eq. (1.11) to the top node in the circuit of Fig. 1.3b, we obtain

$$I_B = I_{R_1} + I_{R_2}$$

Hence, at any node, not all currents can flow into the node—at least one current must flow out of the node. In other words, a node is not a "parking lot" for charges: *the same number of charges that flow into a node must flow out*. This is not unlike a traffic junction, in which the number of cars that flow in must flow out.

### 1.4 Circuit Elements

#### 1.4.1 Resistors

A resistor in a simple circuit is shown in Fig. 1.2. We represent a resistor by its standard zig-zag symbol, as illustrated in Fig. 1.4. Low-resistance resistors which often have to dissipate power in the multiple watts range are usually wire-wound, whereas the more common, higher-resistance resistors are of carbon material in the shape of small cylinders or thin-film strips. Carbon is a nonmetallic material that can have a high resistivity. These resistors can have values up into the megaohm (M $\Omega$ ) range and have small power ratings—typically 1/4, 1/2, and 1 W. For DC, power in a resistor is given by Eq. (1.8), that is,  $P = P_{ave} = I^2 R$ .

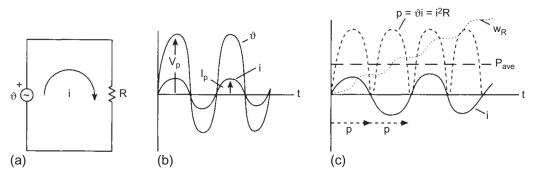

**FIGURE 1.4** (a) A resistor with a voltage  $\nu$  applied. (b) A sinusoidal voltage causes an in-phase sinusoidal current in *R*. (c) Instantaneous power *p* in a resistor is pulsating but is always positive. The dashed arrows suggest that power is always flowing from source to resistor. Energy  $w_R$  continues to increase with time.

Ohm's law  $\nu = Ri$  states that, for a constant *R*, voltage and current in a resistor are in phase. It is assumed that *R* remains a constant for a large range of voltages, currents, and temperatures. The in-phase property is best shown when a sinusoidal voltage is applied to the resistor and the resulting current is sketched, as in Fig. 1.4b.<sup>6</sup>

The current is proportional (in phase) to the applied voltage. In Fig. 1.4c we sketch the instantaneous power  $p = vi = i^2 R$  and note that even though current reverses periodically, p is always positive, implying that power or energy always flows from the source to the resistor, where it is converted into heat and dissipated to the surroundings. The average power delivered to the resistor is obtained by integrating the instantaneous power over a period T of the sinusoid, that is,

$$P_{\text{ave}} = \frac{1}{T} \int_{0}^{T} i^{2} R \, dt = \frac{V_{p}^{2}}{2R} = \frac{RI_{p}^{2}}{2} \tag{1.12}$$

where  $I_p = V_p/R$ . We can now observe that had the resistor been connected to a DC battery of voltage *V*, the power delivered to *R* would have been constant with a value  $P = V \cdot I = I^2 R = V^2/R$ . Hence if we equate DC power  $V^2/R$  to the corresponding average AC power (Eq. 1.12), we conclude that

$$V = \frac{V_p}{\sqrt{2}} = 0.707 V_p \tag{1.13}$$

<sup>&</sup>lt;sup>6</sup>From now on, the instantaneous values of currents or voltages that vary with time will be represented by lowercase letters, whereas uppercase letters will be used for constants such as DC voltage. For example, for the sinusoidal case,  $v = v(t) = V_p \sin t$ , where  $V_p$  is the peak or maximum value of the sine wave. In Fig. 1.4a, the symbol for a sinusoidal source is used, whereas in Figs. 1.1 and 1.2 the symbol for a DC source, i.e., a battery, was used.

This is called the *effective value* of an AC voltage; that is, a sinusoidal voltage of peak value  $V_p$  is as effective in delivering power to a resistor as a DC voltage of value  $V_p/\sqrt{2}$ . Effective or *rms* values will be considered in more detail in the following chapter.

To demonstrate that a resistor continues to absorb energy from a connected source, we can evaluate the energy supplied to a resistor, that is,

$$w_{R} = \int_{0}^{t} p dt' = R \int_{0}^{t} i^{2} dt' = \frac{V_{p}^{2}}{R} \int_{0}^{t} \sin^{2} t' dt' = \frac{V_{p}^{2}}{2R} \left[ t - \frac{\sin 2t}{2} \right]$$

(1.14)

Sketching the last expression of the above equation in Fig. 1.4c shows that *w* continues to increase, wiggling about the average term  $V_p^2 t/2R$ ; this term is equal to Joule's heating law (Eq. 1.9), and when differentiated with respect to time *t* also accounts for the average power given by Eq. (1.12).

#### 1.4.2 Capacitors

A capacitor is a mechanical configuration that accumulates charge q when a voltage v is applied and holds that charge when the voltage is removed. The proportionality constant between charge and voltage is the capacitance *C*, that is,

$$q = Cv \tag{1.15}$$

Many capacitors have a geometry that consists of two conducting parallel plates separated by a small gap. The *C* of such a structure is given by  $C = \varepsilon A/\ell$ , where  $\varepsilon$  is the *permittivity* of the medium between the plates, *A* is the area, and  $\ell$  is the separation of the plates. Figure 1.1 shows such a parallel-plate capacitor (note that the large gap that is shown would result in a small capacitance; in practice, capacitors have a small gap, typically less than 1 mm).

The unit for capacitance is the *farad* (F), which is a rather large capacitance. Most common capacitors have values in the range of microfarads ( $\mu$ F = 10<sup>-6</sup> F), or even picofarads (pF = 10<sup>-12</sup> F), with the majority of practical capacitors ranging between 0.001  $\mu$ F and 10 F. To obtain larger capacitances, we can either increase the area *A*, decrease the spacing  $\ell$ , or use a dielectric medium with larger permittivity  $\epsilon$ . For example, mica and paper have *dielectric constants*<sup>7</sup> of 6 and 2, respectively. Therefore, a parallel-plate capacitor of Fig. 1.1 with mica filling the space between the plates would have a capacitance six times that of a free-space capacitor. Most tubular capacitors are made of two aluminum foil strips, separated by an insulating dielectric medium such as paper or plastic and rolled into log form. It is tempting to keep reducing the spacing between the plates to achieve high capacitance. However, there is a limit, dictated by the dielectric breakdown strength of the insulating material between the plates. When this is exceeded, a spark will jump between the

<sup>&</sup>lt;sup>7</sup>A *dielectric constant* is defined as relative permittivity  $\varepsilon_r = \varepsilon/\varepsilon_0$ , where  $\varepsilon_0 = 8.85 \cdot 10^{-12}$  F/m is the *permittivity* of free space.

#### 10 Electronics and communications for scientists and engineers

plates, usually ruining the capacitor by leaving a conducting track within the insulating material where the spark passed. Hence, knowing the breakdown electric field strength of a dielectric material (for air it is  $3 \cdot 10^4$  V/cm, for paper  $2 \cdot 10^5$  V/cm, and for mica  $6 \cdot 10^6$  V/m) and using Eq. (1.3), which gives the electric field when the voltage and plate separation are specified, we can calculate the voltage which is safe to apply (that which will not cause arcing) to a capacitor of a given plate separation. A practical capacitor, therefore, has stamped on it not just the capacitance but also the voltage. For example, a stamp of 50 V<sub>DC</sub> means, do not exceed 50 V of DC across the capacitor.

To determine how a current passes through a capacitor, we use Eq. (1.15),  $q = C \cdot v$ , differentiate both sides of the equation with respect to time, and note that i = dq/dt; this results in

$$i = C \frac{dv}{dt} \tag{1.16}$$

for the capacitor current, where we have used lowercase letters q, i, and  $\nu$  to denote that charge, current, and voltage can be time-changing and capacitance C is a constant. This expression shows that a constant voltage across a capacitor produces no current through the capacitor (dv/dt = 0). Of course, during the charging phase of a capacitor, the voltage changes and current flows.<sup>8</sup> If we now apply a sinusoidal voltage to the simple capacitor circuit of Fig. 1.5a, we see that the resultant current leads the applied voltage by 90°, or

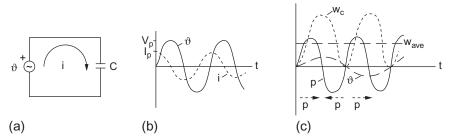

**FIGURE 1.5** (a) A capacitor (depicted by the double line) with voltage  $\nu$  applied, (b) Sinusoidal voltage and current in *C*. (c) Instantaneous power and energy as well as average energy are sketched. (*Note:* amplitudes of *p* and *w*<sub>C</sub> are not to scale.)

<sup>8</sup>During a brief time interval after the capacitor is connected to a battery, a charging current flows through the capacitor, that is, Eq. (1.16) gives a finite value for *i* because the capacitor voltage changes from zero for an initially uncharged capacitor to the battery voltage during charging. During the charging interval, dv/dt is not zero, therefore. Going back to our parallel-plate capacitor of Fig. 1.1, we infer that the charging current moves electrons from left to right through the battery, depositing electrons on the right plate, and leaving the left plate deficient of the same amount of electrons. The electrons on the charged plates do not come from the battery, but from the metallic plates, which have an abundance of free electrons. The battery merely provides the energy to move the charges from one plate to the other. Charging of a capacitor is considered in detail in Section 1.8.

$\nu$  lags *i* by 90°, as shown in Fig. 1.5b. This is easily seen by use of Eq. (1.16): if  $\nu = V_p$  sin *t*, then

$$i = V_p C \cos t = I_p \cos t = I_p \sin (t + \pi/2)$$

The angle of  $\pi/2$  is also referred to as a 90° *degree phase shift*.

The instantaneous power in *C* is given by

$$p = vi = Cv\frac{dv}{dt} = \frac{CV_p^2}{2}\sin 2t \tag{1.17}$$

where  $\sin 2t = 2 \sin t \cos t$  was used. Equation (1.17) is sketched in Fig. 1.5c. The positive and negative values of *p* imply that power flows back and forth, first from source to capacitor, and then from capacitor to source with average power  $P_{ave} = 0$ . The back and forth surging of power, at twice the frequency of the applied voltage, is alluded to by the dashed arrows for *p*. It thus appears that the capacitor, unlike a resistor, does not consume any energy from the source, but merely stores energy for a quarter-period, and then during the next quarter-period gives that energy back to the source. *C* is thus fundamentally different from *R* because *R* dissipates electrical energy as it converts it to heat. *C*, on the other hand, only stores electrical energy (in the charge that is deposited on the plates). To learn more about capacitance let us consider the energy stored in *C*, which is

$$w_{C} = \int p dt = \frac{1}{2} C v^{2} = \frac{C V_{p}^{2}}{2} \sin^{2} t = \frac{C V_{p}^{2}}{4} (1 - \cos 2t)$$

(1.18)

In general, the energy stored in a capacitor is given by the  $Cv^2/2$  term. For the specific case of applied voltage which is sinusoidal, the energy is represented by the last expression in Eq. (1.18). When a sketch of this expression is added to Fig. 1.5c, we see that the average energy,  $CV_p^2/4$ , does not increase with time. That is, the energy only pulsates as it builds up and decreases again to zero. If one compares this to the corresponding sketch for a resistor, Fig. 1.4c, one sees that for an energy-converting device, which *R* is, energy steadily increases with time as *R* continues to absorb energy from the source and convert it to heat.

#### Example 1.1

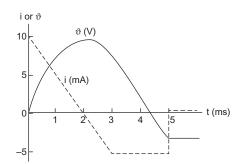

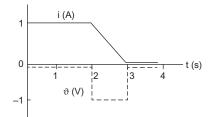

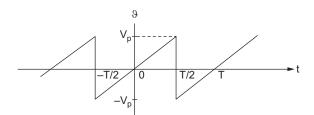

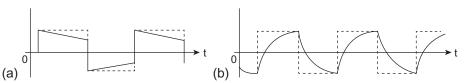

An initially uncharged 1  $\mu$ F capacitor has a current, shown in Fig. 1.6, flowing through it. Determine and plot the voltage across the capacitor produced by this current.

Integrating the expression i = C dv/dt, we obtain for the voltage

$$v = \frac{1}{C} \int_{-\infty}^{t} i dt = \frac{1}{C} \int_{0}^{t} i dt + V_0$$

where  $V_0$  is the initial voltage on the capacitor due to an initial charge. For 0 < t < 3 ms, the current represented by the straight line is i = 0.01 - 5t, and since  $V_0 = 0$  we obtain

$v = 10^4 (1 - 250t)t$

FIGURE 1.6 The dotted line is the capacitor current. The resultant voltage is represented by the solid line.

which is an equation of a parabola. At t = 2, 3 ms, voltage is  $\nu = 10, 7.5$  V. For 3 < t < 5 ms, i = -5 mA, which yields

$$v = \frac{1}{C} \int_{3}^{t} i dt + V_0 = -5(t-3) + 7.5$$

and which sketches as the straight line. For t > 5 ms, i = 0 and the voltage remains a constant,  $\nu = -2.5$  V.

We can now summarize the characteristics of capacitors:

- Only a voltage that changes with time will produce a current through a capacitor. A capacitor is therefore an open circuit for direct current (DC).

- Since energy cannot change instantaneously (it is a continuous function of time), and since the energy stored in a capacitor is expressed in terms of voltage as  $\frac{1}{2}Cv^2$ , we conclude that voltage across a capacitor cannot change instantaneously (unless we want to entertain infinite currents, which is not practical). Capacitance has therefore smoothing properties for voltage, which has many important applications such as in filter design.

- A finite amount of energy can be stored, but because no mechanism for energy dissipation exists in an ideal capacitor none can be dissipated. For sinusoidal time variations this is easily seen since the 90° phase difference between current and voltage results in Expression (1.17), which gives  $P_{ave} = 0$ .

### 1.4.3 Inductors

The last of the common circuit elements is the inductor. Like a capacitor, it is an energystorage device, and like a capacitor which stores the energy in its electric field between the plates, an inductor stores it in its *magnetic field*, which surrounds the inductor. As this is a book on electronics, we will not pursue the field interpretation of energy storage, but instead use the voltage and current which create these fields in capacitors and inductors, respectively. Thus we can say that a capacitor stores energy in the charges which are created when a voltage is applied to a capacitor, giving rise to the energy expression in terms of voltage, which from Eq. (1.18) is  $w_C = \frac{1}{2}Cv^2$ . Similarly, since current causes a magnetic field, we can derive the expression  $w_L = \frac{1}{2}Li^2$ , which gives the energy stored in an inductor, where *i* is the current flowing through the inductor and *L* is the inductance of the inductor (note the duality of these two expressions: *C* is to *L* as  $\nu$  is to *i*).

To derive the above formula, we begin with the notion that inductance *L*, like capacitance *C*, is a property of a physical arrangement of conductors. Even though any arrangement possesses some inductance, there are optimum arrangements that produce a large inductance in a small space, such as coils, which consist of many turns of fine wire, usually wound in many layers, very much like a spool of yarn. The definition of inductance rests on the concept of flux linkage. This is not a very precise concept unless one is willing to introduce a complicated topological description. For our purposes, it is sufficient to state that flux linkage  $\Phi$  is equal to the magnetic flux that exists inside a coil multiplied by the number of turns of the coil. Inductance *L* is then defined as  $L = \Phi/i$  (which is analogous to capacitance C = q/v), where *i* is the current in the coil that gives rise to the magnetic field B of the coil (Note: magnetic flux (Wb) = magnetic field B (Wb/m<sup>2</sup>)·area *A* (m<sup>2</sup>)). Recalling *Faraday's law*,  $v = d\Phi/dt = d(NBA)/dt$  which gives the induced voltage *v* in a coil when the coil is in a time-changing magnetic field, we obtain

$$v = L \frac{di}{dt} \tag{1.19}$$

which is the defining equation for voltage and current in an inductance *L* (similar to the defining equation v = Ri for a resistor, and i = Cdv/dt for a capacitor). Again, as in the case of *C* and *R*, we assume that *L* remains constant over a large range of voltages and currents.

The unit for inductance is the *Henry* (H). Inductors for filter applications in power supplies are usually wire-wound solenoids on an iron core with inductances in the range from 1 to 10 H. Inductors found in high-frequency circuits are air-core solenoids with values in the milli-Henry (mH) range or lower.

As in the case of capacitance, where a typical capacitor consisted of two parallel metallic plates of area A, separated by a distance  $\ell$  and had capacitance  $C = \epsilon A/\ell$ , we can state that a typical inductor is a wire-wound coil (solenoid) of cross-section A, length  $\ell$  and Nturns. To find the inductance L of such a coil we use Faraday's law and Ampere's law and obtain

$$L = \Phi/i = NBA/i = N\mu HA/i = N\mu (Ni/\ell)A/i = \mu N^2 A/\ell$$

The inductance is seen to be proportional to the number of turns squared but also the insertion of a ferromagnetic core such as iron which can have a  $\mu$  many thousands that of free space can greatly increase inductance.

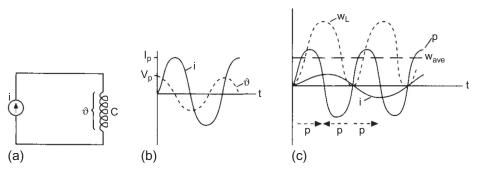

As in the case of capacitance, assuming sinusoidal variations will quickly show the characteristics of inductance. If (as shown in Fig. 1.7a) a current source which produces a current  $i = I_p \sin t$  is connected to an inductor *L*, then using Eq. (1.19), voltage across the inductor will be  $\nu = LI_p \cos t$ , which is sketched in Fig. 1.7b. Hence, for sinusoidal

**FIGURE 1.7** (a) An inductor (depicted by a spiral symbol) with current *i* applied, (b) Sinusoidal voltage and current in *L*. (c) Sketches of instantaneous power and energy, and average energy. (*Note*: amplitudes of p and  $w_{L}$  are not to scale.)

variation, voltage leads current by 90°, or *i* lags  $\nu$  by the same amount in *L*. The instantaneous power is

$$p = vi = Li\frac{di}{dt} = \frac{LI_p^2}{2}\sin 2t \tag{1.20}$$

The positive and negative values of p imply that power<sup>9</sup> flows back and forth between the source and the inductor. Hence, like the capacitor, an inductor accepts energy from the source for a quarter-period and returns the energy back to the source over the next quarter-period. This is nicely illustrated when we consider energy, which is

$$w_L = \int p dt = \frac{1}{2} L i^2 = \frac{L I_p^2}{2} \sin^2 t \tag{1.21}$$

In general, the energy stored in an inductor is given by the  $Lt^2/2$  term. For the sinusoidal case, the last term shows that the energy increases as the inductor accepts energy from the source and decreases again to zero as the inductor returns the stored energy to the source. This is illustrated in Fig. 1.7c. An example of large-scale energy storage is a new technology which will enable industry to store cheap, off-peak electrical energy in superconducting coils for use during periods of high demand. A large, steady current is built up in a coil during off-peak periods, representing  $Lt^2/2$  of energy that is available for later use.

#### Example 1.2

A 1 H inductor has an initial 1 A current flowing through it, i.e.,  $i(t = 0) = I_0 = 1$  A. If the voltage across *L* is as shown in Fig. 1.8, determine the current through the inductor. Integrating the expression  $\nu = Ldi/dt$ , we obtain for the current

$$i = \frac{1}{L} \int_{-\infty}^{t} v \, dt = \frac{1}{L} \int_{0}^{t} v \, dt + I_0$$

<sup>9</sup>Strictly speaking, it is the *energy* that flows back and forth and power is the time rate of change of energy. However, when describing flow, the terms power and energy are used interchangeably in the popular literature.

FIGURE 1.8 Current and voltage waveforms in a 1 H inductor.

For 0 < t < 2 s, we have  $i = I_0 = 1$  A, because  $\nu = 0$  as shown in the figure. For 2 s < t < 3 s,

$$i = \int_{2}^{t} (-1)dt + I_0 = 3 - t$$

which gives the downward-sloping straight line for the current. For t = 3 s, i = 0, and for t > 3 s, the current remains at zero, i.e., i = 0, as the voltage for t > 3 s is given as  $\nu = 0$ .

This example demonstrates that even though the voltage makes finite jumps, the current changes continuously in an inductor.

The characteristics of inductors can be summarized as follows:

- Only a current that changes with time can produce a voltage across an inductor. An inductor is therefore a short circuit for DC. Very high voltages can be produced across an inductor when the current through *L* is suddenly interrupted (an arc can form at the point of interruption, if the interruption is too sudden).

- As the energy (which cannot change instantaneously) stored in an inductor is given by  $W_{\rm L} = \frac{1}{2}LI^2$ , we conclude that current through an inductor also cannot change instantaneously—unless we want to consider infinite voltages, which is not practical. Inductance has therefore smoothing properties for current. An inductor, for example, inserted in a circuit that carries a fluctuating current will smooth the fluctuations.

- A finite amount of energy can be stored, but because no mechanism for energy dissipation exists in an ideal inductor none can be dissipated.

#### 1.4.4 Batteries

Joule's law states that a resistor carrying a current generates heat. The electrical energy is frequently supplied to the resistor by a battery, which in turn obtains its energy from chemical reactions within the battery. Hence, heat generation by *R* involves two transformations: from chemical to electrical to heat. The symbol for a battery is shown in Fig. 1.1 and in Fig. 1.9a, with the longer bar denoting the positive polarity of the battery terminals. Batteries are important sources of electrical energy when a constant voltage is desired.

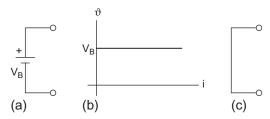

Before we analyze practical batteries, let us first characterize ideal batteries or ideal voltage sources. An ideal battery is defined as one that maintains a constant voltage,

FIGURE 1.9 (a) An ideal battery. (b) The output characteristics of an ideal battery. (c) The internal resistance of an ideal battery is that of a short circuit.

say,  $V_{\rm B}$ , across its terminals, whether a current is flowing or not. Hence, voltage  $V_{\rm B}$  of an ideal battery is completely independent of the current, as shown in Fig. 1.9b. Such a source is also referred to as an *independent source* (a source connected in a circuit is said to be independent if its value can be assigned arbitrarily<sup>10</sup>. Since an ideal battery will maintain a voltage  $V_{\rm B}$  across its terminals even when short-circuited,<sup>11</sup> we conclude that such a source can deliver, in theory, infinite power (since  $P = V^2/R$ , as  $R \to 0$ ,  $P \to \infty$ ). Hence, the name *ideal source*. We also observe that the slope of the  $\nu$ -*i* curve in Fig. 1.9b is zero. Applying Ohm's law, R = V/I, to such a horizontal  $\nu$ -*i* line implies zero resistance. We therefore conclude that the internal resistance of an ideal source is zero. This explains why an ideal battery causes infinite current when short-circuited. Ignoring difficulties that infinities create, we learn that when looking into the terminals of an ideal battery, we see a short circuit (we are now using common circuits language). Saying it another way, if we somehow could turn a dial and decrease the voltage  $V_{\rm B}$  of the ideal battery to zero, we would be left with a short circuit as shown in Fig. 1.9c.

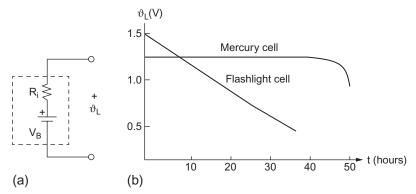

It is common to represent voltage sources in circuit schematics by ideal sources, which is fine as long as there are no paths in the schematic that short such sources (if there are, then the schematic is faulty and does not represent an actual circuit anyhow). Practical sources, on the other hand, always have finite internal resistance, as shown in Fig. 1.10a, which limits the current to non-infinite values should the battery be shortcircuited. Of course  $R_i$  is not a real resistor inside the battery, but is an abstraction of the chemistry of a real battery and accounts for the decrease of the terminal voltage when the load current increases. The internal voltage  $V_B$  is also referred to as the *electromotive force* (emf ) of the battery. From our previous discussion, we easily deduce that powerful batteries are characterized by low internal resistance (0.005  $\Omega$  for a fully charged car battery), and smaller, less powerful batteries by larger internal resistance (0.15  $\Omega$  for an alkaline flashlight battery, size "C").

<sup>&</sup>lt;sup>10</sup>There are special kind of sources in which the source voltage depends on a current or voltage elsewhere in the circuit. Such sources will be termed dependent sources or controlled sources.

<sup>&</sup>lt;sup>11</sup>A short circuit is a zero-resistance path (current can flow but voltage across the path is zero). For example, a piece of copper wire can be considered as a short-circuit element. The opposite of a short is an open circuit, which is an infinite resistance path (voltage can exist across the path but current is zero). These two elements are modeled by the two positions of an on–off switch.

**FIGURE 1.10** (a) A practical battery with  $emf V_B$  and internal resistance  $R_i$ . (b) Discharge characteristics of two types of batteries.

Another characteristic of practical batteries is their increasing internal resistance with discharge. For example, Fig. 1.10b shows the terminal voltages versus hours of continuous use for two types. The mercury cell maintains its voltage at a substantially constant level of 1.35 V over its lifetime (but drops sharply when the battery is exhausted) in comparison to ordinary flashlight cells which start out at 1.55 V but decrease continually with use. Other types (lithium, 3.7 V, very long shelf life of over 10 years; nickel-cadmium, 1.25 V, sealed but rechargeable; lead-acid, 2 V, powerful and rechargeable, used as car batteries when connected in series as three-cell 6 V or six-cell 12 V units) fall somewhere between the two curves. The rate of decrease of available voltage as the battery discharges is determined by the chemical reaction within the battery. While battery chemistry is beyond the scope of this book, what is of interest to us is that the decreasing chemical activity during discharge can be associated with an increase of internal battery resistance. Hence, a fully charged battery can be viewed as possessing a low internal resistance, which gradually increases with battery use and becomes very large for a discharged battery.

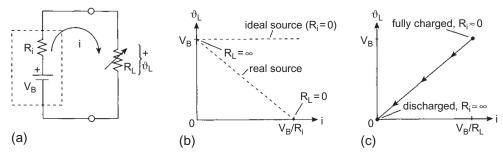

Figure 1.11a shows a circuit in which a practical battery is connected to a load, represented by  $R_L$ , and delivers power to the load.  $R_L$  can be the equivalent resistance of a radio,

FIGURE 1.11 (a) A practical battery with a variable load connected, (b) Characteristics of a source with increasing load, (c) Characteristics of a source being depleted.

a TV set, or any other electrical apparatus or machinery which is to be powered by the battery. The power available to the load is given by  $i^2 R_L$ . However, since the battery has an internal resistance, energy will also be dissipated within the battery. The internal loss is given by  $i^2 R_i$  and will show up as internal heat. It is therefore dangerous to short a powerful battery, as all of the available energy of the battery will then be rapidly converted to internal heat and, unless the shorting element melts rapidly, a dangerous explosion is possible.

Let us now assume, for the time being, that  $R_i$ , is constant but the load  $R_L$  is variable (represented by the arrow across  $R_L$  in Fig. 1.11a) and analyze the circuit as the burden on the battery is increased. Using Kirchhoff's voltage law (Eq. 1.10), we obtain for the circuit

$$V_B = iR_i + iR_L \tag{1.22}$$

The voltage across the load resistor,  $\nu_{\rm L} = iR_{\rm L}$ , which is also the available voltage across the external battery terminals, is given from Eq. (1.22) as

$$v_L = V_B - iR_i \tag{1.23}$$

This is an equation of a straight line with constant slope of  $-R_i$  and is plotted in Fig. 1.11b. The available voltage is therefore the emf of the battery minus the internal voltage drop of the battery. The current that flows in the series circuit is obtained from Eq. (1.22) as

$$i = \frac{V_B}{R_i + R_L} \tag{1.24}$$

As the load resistance  $R_L$  decreases, the burden on the battery increases. As shown in Fig. 1.11b, this is accompanied by a decrease in the available voltage  $\nu_L$ , usually an undesirable result. Eliminating *i* from Eqs. (1.23) and (1.24) to give

$$v_L = V_B \frac{R_L}{R_i + R_L} \tag{1.25}$$

shows the decrease of  $\nu_{\rm L}$  from  $V_{\rm B}$  as  $R_{\rm L}$  is decreased. Thus, when there is no load on the battery ( $R_{\rm L}$  is very large), the available voltage is maximum at  $\nu_{\rm L} \approx V_{\rm B}$ , but for a large load ( $R_{\rm L} \approx 0$ ), the available voltage drops to  $\nu_{\rm L} \approx 0$ . Utility companies, for example, have difficulty maintaining constant voltage during summer when the demand for electricity increases mostly because of energy-hungry air conditioning equipment.<sup>12</sup> Lower-thannormal voltage conditions (popularly referred to as brownouts) put an abnormal strain on customers' electrical equipment which leads to overheating and eventually to failure.<sup>13</sup>

<sup>12</sup>The circuit of Fig. 1.11b is a general representation of power delivery at a constant voltage. It applies to a flashlight battery delivering power to a bulb, a solar cell powering a calculator, a car battery starting an automobile, or a power utility delivering power to homes. All these systems have an internal emf and an internal resistance, irrespective of AC or DC power produced.

<sup>13</sup>Overheating results when the voltage for an electric motor decreases, thereby increasing the current in the motor so as to preserve the power ( $p = \nu i$ ) of the motor. The increased current leads to increased  $I^2 R$  losses in the windings of the motor, which in turn leads to an increase in generated heat that must be dissipated to the surroundings.

An obvious solution to brownouts is to decrease the internal resistance  $R_i$  of the generating equipment as this would decrease the slope of the curve in Fig. 1.11b by moving the intersection point  $V_{\rm B}/R_i$ , to the right, thus bringing the curve closer to that of an ideal source of Fig. 1.9b. Of course, low- $R_i$  equipment means larger and more expensive generators.

To obtain Fig. 1.11b we have assumed that the internal resistance  $R_i$  remains constant as the load resistance  $R_L$  changes. Let us now consider the case when load  $R_L$  remains constant but  $R_i$  changes. An example of this is a battery being discharged by a turned-on flashlight which is left on until the battery is depleted. Figure 1.11c gives the  $\nu$ -*i* curve for battery discharge with the arrows indicating the progression of discharge. We see that the fully charged battery, starting out with a small internal resistance ( $R_i \approx 0$ ), can deliver a current  $i \approx V_B/R_L$  and a voltage  $\nu_L \approx V_B$ . After discharge, ( $R_i \approx \infty$ ), the current (Eq. 1.24) and terminal voltage (Eq. 1.25) are both zero.

In summary, one can say that the reason that current goes to zero as the battery is discharged is not that the emf, whose magnitude is given by  $V_{\rm B}$ , goes to zero, but that the internal resistance  $R_i$  changes to a very large value. A discharged battery can be assumed to still have its emf intact but with an internal resistance which has become very large.  $R_i$  is therefore a variable depending on the state of the charge and the age (shelf life) of the battery.

To measure the emf of the battery, we remove the load, i.e., we open-circuit the battery and as the current *i* vanishes we obtain from Eq. (1.23) that  $\nu_{\rm L} = V_{\rm B}$ ; the voltage appearing across the battery terminals on an open circuit is the battery's emf. To measure the emf, even of an almost completely discharged battery, one can connect a high-resistance voltmeter (of 10<sup>7</sup>  $\Omega$ or larger) across the battery terminals. Such a voltmeter approximates an open-circuit load and requires only the tiniest trickle of charge flow to give a reading. If the input resistance of the meter is much larger than  $R_{ij}$  the reading will be a measure of the  $V_{\rm B}$  of the battery.

To measure the  $R_i$  of a battery, one can short-circuit the battery, for only a very brief time, by connecting an ammeter across the battery and reading the short-circuit current. (As this is a dangerous procedure, it should be done only with less powerful batteries, such as flashlight cells. It can also burn out the ammeter unless the appropriate high-ampere scale on the meter is used.) The internal resistance is then given by  $V_{\rm B}/I_{sc}$ . A less risky procedure is to connect a variable resistance across the battery and measure the voltage  $\nu_{\rm L}$ . Continue varying the resistance until the voltage is half of  $V_{\rm B}$ . At this point the variable resistance is equal to  $R_i$ . If this is still too risky—as it puts too low a resistance across the battery—consider the procedure in the following example.

#### Example 1.3

Determine the  $R_i$  of an alkaline battery (size C) by loading the cell with a 1  $\Omega$  resistor.

Consider Fig. 1.11a. It is known that  $V_{\rm B}$  for an alkaline cell is 1.5 V. Measuring the voltage across the 1  $\Omega$  resistor, we obtain 1.3 V, which must leave a voltage drop of 0.2 V across  $R_i$ . As the current in the circuit is given by i = 1.3 V/1  $\Omega = 1.3$  A, we obtain for the internal resistance  $R_i = 0.2$  V/l.3 A  $\cong 0.15 \Omega$ .

#### 1.4.5 Voltage and Current Sources

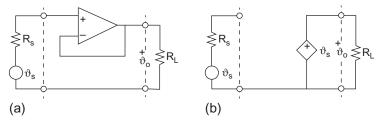

*Voltage sources* in general provide voltages that can vary with time such as sinusoids and square waves, or that can be constant with time such as the voltage of a battery. In either case, the principles that were covered for batteries in the previous section apply equally well to voltage sources in general. That is, each type of voltage source has an ideal source in series with an internal resistance as shown in Fig. 1.12a. Note the new circuit symbol for an independent voltage source, which includes a battery as a special case by simply specifying that  $\nu_s = 12$  V for a 12 V battery, for example.

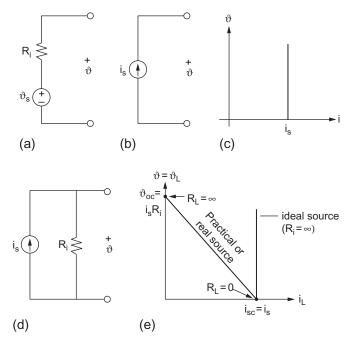

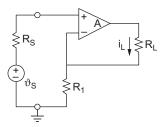

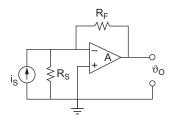

A second type of source, known as a *current source*, whose symbol is shown in Fig. 1.12b, produces a constant current output independent of voltage, as shown in Fig. 1.12c. A vertical  $\nu$ -*i* graph implies that the internal resistance of a current source is *infinite* (in contrast to a voltage source for which it is *zero*), i.e., if we somehow could turn a dial and reduce the amplitude  $i_s$  to zero, we would be left with an open circuit. This, of course, is again an ideal source, nonexistent in the real world, as it appears to supply infinite power. For example, connecting a load resistor  $R_L$  of infinite resistance (that is, an open circuit) to a current source would produce power  $p = i_s^2 R_L$ , which is infinite, as by definition the ideal current source will maintain  $i_s$  current through the open circuit. Therefore, a practical current source always appears with an internal resistance which parallels

**FIGURE 1.12** (a) A practical voltage source. (b) An ideal current source. (c) The  $\nu$ -*i* characteristics of an ideal current source, (d) A practical current source, (e) Load voltage  $\nu_L$  and load current  $i_L$  variation as the load resistor  $R_L$  changes, for the case when  $R_L$  is connected to the practical source of Fig. 1.12d.

the ideal current source, as shown in Fig. 1.12d. Now, leaving the output terminals opencircuited, as shown in Fig. 1.12d,  $i_s$  simply circulates through  $R_i$ . Practical examples of current sources are certain transistors which can maintain a constant current, similar to that shown in Fig. 1.12c, for a wide range of load resistances. However, when  $R_L$  begins to exceed a certain value, the current drops sharply.

To obtain the output characteristics, we connect a load resistance  $R_L$  to the real current source of Fig. 1.12d. Now the source current  $i_s$  will divide between resistors  $R_i$  and  $R_L$ . If we vary  $R_L$  and plot the  $\nu_L$ - $i_L$  graph, we obtain Fig. 1.12e. This graph, like the respective one for a voltage source, Fig. 1.11b, shows that as we decrease  $R_L$ , the load voltage  $\nu_L$  decreases and drops to zero for  $R_L = 0$ , at which point the current through the load resistor, which is now a short circuit, becomes  $i_L = i_{sc} = i_s$ . On the other hand, when  $R_L$  is infinite, i.e., an open circuit, the load voltage is  $\nu_L = \nu_{oc} = i_s R_i$ .

#### 1.4.6 Source Equivalence and Transformation

From the standpoint of the load resistor, it is immaterial if a current or a voltage source is delivering power to  $R_{\rm L}$ . If, for example, 10 W is being delivered to a load resistance by a source that is enclosed in a black box, there is no way of knowing if the hidden source is a voltage or a current source. An equivalence between current and voltage sources must therefore exist, which we now define by stating that if two separate sources produce the same values of  $\nu$  and i in  $R_{\rm L}$ , then for electrical purposes the two sources are equivalent. The equivalence must hold for any load resistance, including  $R_{\rm L} = 0$  and  $R_{\rm L} = \infty$ ; in other words, if two sources produce the same short-circuit current,  $I_{sc}$ , when  $R_{\rm L} = 0$ , and the same open-circuit voltage,  $V_{oc}$ , when  $R_{\rm L} = \infty$ , then the sources are equivalent.

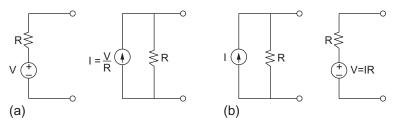

With the above statement of equivalence, we now have a convenient and quick way to transform between sources. For example, if we begin with the practical voltage source of Fig. 1.13a, we readily see that  $I_{sc} = V/R$ , and from Eq. (1.25),  $V_{oc} = V$ . Therefore, the equivalent practical current source, shown in Fig. 1.13a, has a current source of strength I = V/R in parallel with a resistance R. Similarly, if we start out with a current source and would like to find the equivalent voltage source, Fig. 1.13b shows that the current source of strength I in parallel with R gives  $I_{sc} = I$  when short-circuited and  $V_{oc} = IR$  when open-circuited. Therefore, the equivalent voltage source is easily obtained and is shown in Fig. 1.13b.

FIGURE 1.13 (a) A voltage source and its current source equivalent. (b) A current source and its voltage source equivalent.

Summarizing, we observe that under open-circuit conditions,  $V_{oc}$  always gives the voltage element (emf) of an equivalent voltage source, whereas under short-circuit conditions,  $I_{sc}$  always gives the current element of an equivalent current source. Furthermore, we easily deduce that the source resistance is always given by  $R = V_{oc}/I_{sc}$ . If we examine Fig. 1.13, we note that the source resistance is R and is the same for all four equivalents. That is, looking back into the terminals of the voltage source we see only resistance R, because the voltage source element, which is in series with R, is equivalent to a short (see Fig. 1.9c). Similarly, looking into the terminals of the current source, we see R, because the current source element itself, which is in parallel with R, is equivalent to an open circuit.

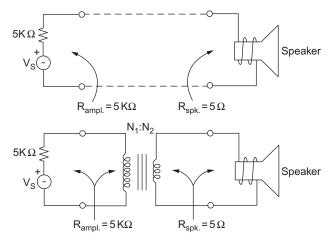

Open-circuit and short-circuit conditions, therefore, provide us with a powerful tool to represent complicated sources by the simple, equivalent sources of Fig. 1.13. For example, an audio amplifier is a source that provides amplified sound and therefore can be represented at the output terminals of the amplifier by one of the equivalent sources. To be able to view a complicated piece of equipment such as an amplifier simply as a voltage source in series with a resistance aids in the understanding and analysis of complex electronics. In the case of the audio amplifier, the equivalent source resistance is the output resistance of the amplifier, which for maximum power output to the speakers needs to be matched<sup>14</sup> to the impedance of the speakers that will be powered by the audio amplifier.

## 1.5 Series and Parallel Circuits

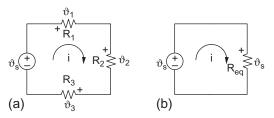

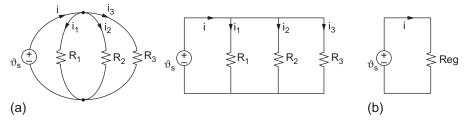

Although we have already presented such circuits when discussing Kirchhoff's laws (see Fig. 1.3), we will now consider them in detail. The series circuit in Fig. 1.3a was drawn in the shape of a loop. However, from now on we will use rectangular shapes for circuits as they appear neater and are easier to trace in complicated circuits. Figure 1.14a shows a voltage source and three resistors in a series circuit which we will now show to be equivalent to the one-resistor circuit of Fig. 1.14b by observing that the current is the same in every component of the circuit. Using Kirchhoff's voltage law, we obtain

FIGURE 1.14 (a) A series circuit and (b) its equivalent.

<sup>14</sup>Matching will be considered in detail in Section 1.6.5, Maximum Power Transfer and Matching.

$$v_{s} = v_{1} + v_{2} + v_{3}$$

=  $R_{1}i + R_{2}i + R_{3}i$

=  $i(R_{1} + R_{2} + R_{3})$

=  $i(R_{eq})$  (1.26)

for the circuit of Fig. 1.14a, and similarly we obtain  $\nu_s = iR_{eq}$  for the circuit in Fig. 1.14b. Hence, comparing, we conclude that the equivalent resistance of *N* resistors in series is

$$R_{\rm eq} = R_1 + R_2 + \dots + R_N \tag{1.27}$$

To the source, a series of resistors or a single equivalent resistor is the same, i.e., the  $\nu$ -*i* relationship is the same.

In review, we should note that small-case letters are used to denote quantities that could be time-varying ( $\nu_s = V \sin t$ ), whereas capital letters denote constant quantities, such as those for a 12 V battery ( $V_B = 12$  V). However, constant quantities can also be expressed by using small-case letters; e.g., the 12 V battery can be equally well referred to as  $\nu_s = 12$  V. Convention is to use the battery symbol when the voltage is produced by chemical action, but when a constant voltage is provided by a power supply or by a signal generator, which can produce time-varying voltages and constant ones, the voltage source symbol of Fig. 1.14 is appropriate. Another review point is the polarity convention, which has the current arrow pointing at the plus when the voltage is that of a sink (voltage drop), and at the minus when it is a source (voltage rise). The following example demonstrates these points.

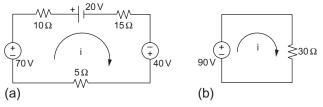

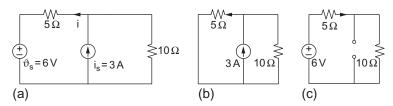

# Example 1.4

Three sources are connected to a series of resistors as shown in Fig. 1.15a. Simplify the circuit and find the power delivered by the sources. Using Kirchhoff's voltage law to sum the voltages' drops and rises around the loop, we have, starting with the 70 V source,

$$-70 + 10i + 20 + 15i - 40 + 5i = 0$$

$-90 + 30i = 0$

$i = 3A$

The loop current is therefore 3 A and the equivalent circuit is the two-element circuit of Fig. 1.15b. The power consumed by the resistors is  $i^2 R = 3^2 \cdot 30 = 270$  W, which is also the power produced by the equivalent source (90 V·3 A = 270 W). The individual sources produce

FIGURE 1.15 (a) A series circuit and (b) its equivalent.

70.3 = 210 W, -20.3 = -60 W, and 40.3 = 120 W. Clearly, the 20 V battery acts as a load—it is being charged by the remaining two sources at the rate of 60 W.

A second way of connecting elements was shown in Fig. 1.3b, when discussing Kirchhoff's current law. In such a parallel arrangement we see that the voltage is the same across both resistors, but the currents through the elements will be different. Let us consider the slightly more complicated, but still two-node, circuit shown in Fig. 1.16a. Summing currents at the top node, we have

$$i = i_1 + i_2 + i_3 \tag{1.28}$$

i.e., the sum of the three currents  $i_1 = v_s/R_1$ ,  $i_2 = v_s/R_2$ , and  $i_3 = v_s/R_3$  equals the source current *i*. Substituting for the resistor currents in Eq. (1.28), we obtain

$$i = v_s \left(\frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}\right) \tag{1.29}$$

The terms in the parentheses can be identified as the equivalent resistance of the parallel resistors. Using Ohm's law, we can define

$$i = v_s \frac{1}{R_{\rm eq}} \tag{1.30}$$

Hence, the equivalent resistance is

$$\frac{1}{R_{\rm eq}} = \frac{1}{R_1} + \frac{1}{R_2} + \frac{1}{R_3}$$

(1.31)

and the equivalent circuit is shown in Fig. 1.16b. Equation (1.31) is an often-used expression that is readily extended to N resistors in parallel. Particularly useful is the two-resistors-in-parallel expression

$$R_{\rm eq} = R_1 \| R_2 = \frac{R_1 R_2}{R_1 + R_2} \tag{1.32}$$

which is needed often and should be memorized. For example, a 1 k $\Omega$  and a 10 k $\Omega$  resistor in parallel are equal to an equivalent resistor of 0.91 k $\Omega$ ; i.e., two resistors in parallel have a resistance that is less than the smallest resistance.

FIGURE 1.16 (a) Two ways of drawing a two-node circuit of a voltage source and three resistors in parallel. (b) The equivalent circuit.

The analysis for resistors in parallel is somewhat easier if we make use of conductance *G*, which is defined as G = 1/R. Ohm's law can then be written as i = Gv, and Eq. (1.28) becomes

$$i = \nu_s (G_1 + G_2 + G_3) \tag{1.33}$$

Hence, conductances in parallel add, or

$$G_{\rm eq} = G_1 + G_2 + G_3 \tag{1.34}$$

and Eq. (1.34) is equal to Eq. (1.31), as  $G_{eq} = l/R_{eq}$ .

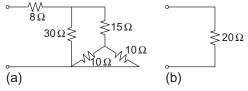

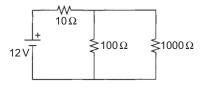

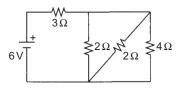

#### Example 1.5

Simplify the network of resistors shown in Fig. 1.17a, using the rules of series and parallel equivalents.

First, combine the 10  $\Omega$  resistors which are in parallel to give 5  $\Omega$ . Now combine this 5  $\Omega$  resistor with the 15  $\Omega$  resistor, which are in series, to give 20  $\Omega$ . Now combine the equivalent 20  $\Omega$  resistor which is in parallel with the 30  $\Omega$  resistor of the network to give 12  $\Omega$ . Finish by combining the equivalent 12  $\Omega$  resistor with the remaining 8  $\Omega$  resistor, which are in series, to give 20  $\Omega$ , which is the simplified network shown in Fig. 1.17b.

FIGURE 1.17 (a) A network of resistors and (b) its reduced equivalent.

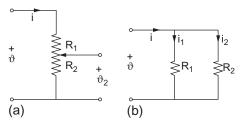

#### 1.5.1 Voltage and Current Division

Practical circuits such as volume controls in receivers use voltage divider circuits, such as that shown in Fig. 1.18a (also known as a *potentiometer*), where the tap is movable for a continuous reduction of the voltage  $\nu$ . The voltage source  $\nu$  sees a resistance

FIGURE 1.18 (a) A voltage divider and (b) a current divider circuit.

which is  $R_1 + R_2$ , and  $\nu_2$  is the voltage drop across the  $R_2$  portion of the potentiometer. The current *i* flowing due to  $\nu$  is  $i = \nu/(R_1 + R_2)$ ; therefore the output voltage  $\nu_2$  is equal to  $iR_2$ , or

$$v_2 = v \frac{R_2}{R_1 + R_2} \tag{1.35}$$

which is the voltage-divider equation.

Equally useful, but more subtle, is current division. Figure 1.18b shows a current *i* that divides into two components  $i_1$  and  $i_2$ . To find the component currents we first determine *i* as

$$i = \frac{v}{R_1 \| R_2} = v \frac{R_1 + R_2}{R_1 R_2} \tag{1.36}$$

The current through  $R_1$  and  $R_2$  is simply given by  $\nu/R_1$  and  $\nu/R_2$ , respectively, which by use of Eq. (1.36) is

$$i_1 = i \frac{R_2}{R_1 + R_2} \tag{1.37}$$

and

$$i_2 = i \frac{R_1}{R_1 + R_2} \tag{1.38}$$

The above two equations establish the rules of current division. Although not as straight forward as voltage division, current division at the junction of two resistors follows the rule that the larger current flows through the smaller resistor. In the limit, for example, when  $R_1$  is a short, all the current flows through  $R_1$  and none through  $R_2$ , in agreement with Eq. (1.38), which states that ( $i_2 = 0$  for this case. When analyzing circuits, we need to have at our fingertips the rules of voltage and current division, which makes these rules worth memorizing.

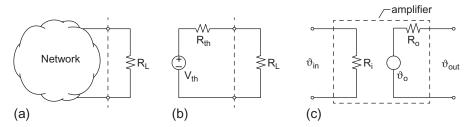

## 1.6 Network Simplification

We have already simplified some circuits by applying the rules of series and parallel circuits. When considering more complicated circuits, usually referred to as networks, there are other, more sophisticated analysis tools at our disposal which we need to study and be able to apply. In electronics, we frequently encounter *one-port* and *two-port* devices. A one-port is a two-terminal circuit such as those shown in Fig. 1.13 or in Fig. 1.20. Two-ports are of great interest, because complicated electronic equipment can frequently be viewed as two-ports. For example, connections to an audio amplifier are made at the input and the output terminals. At the input, we connect a pickup device, whose weak signal is incapable of driving a speaker and therefore needs to be amplified. At the output, the amplifier acts as a powerful source and can easily drive a speaker that is connected to the output terminals. Hence, from the viewpoint of the user, a two-port depiction of an

amplifier is all that is needed. Furthermore, without having yet studied amplifiers, we can already deduce a fundamental circuit for an amplifier: at the output port, the amplifier must look like a practical source. We now have a simple, but highly useful, threecomponent model of an amplifier delivering power to a load: a voltage source in series with a source resistance is connected to a load such as a speaker which is represented by  $R_L$ . This simple circuit looks like that of Fig. 1.11a (with the battery replaced by a voltage source) and is a valid representation of an amplifier at the output terminals. We will consider now several theorems, including Thevenin's, which will formalize the replacing of all or part of a network with simpler equivalent circuits.

### 1.6.1 Equivalence

We have already referred to equivalence in the subsection on Source Equivalence and Transformation. To repeat: two one-port circuits are equivalent if they have the same  $\nu$ -*i* characteristics at their terminals.

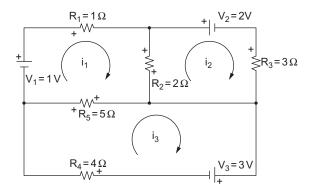

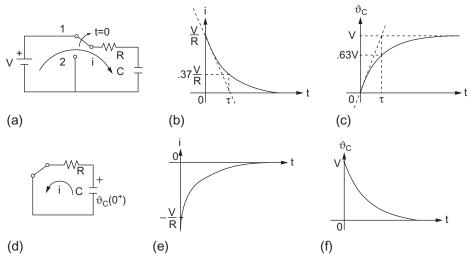

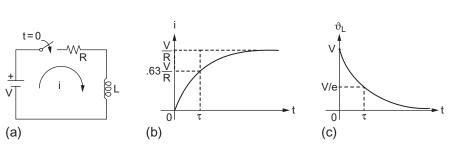

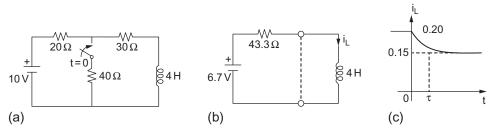

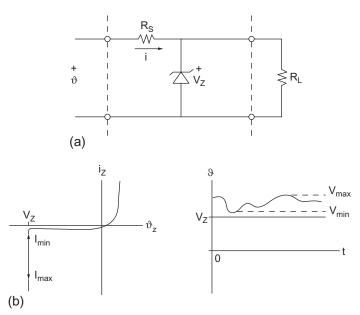

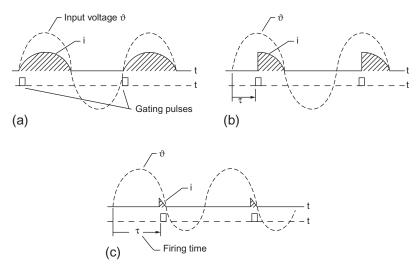

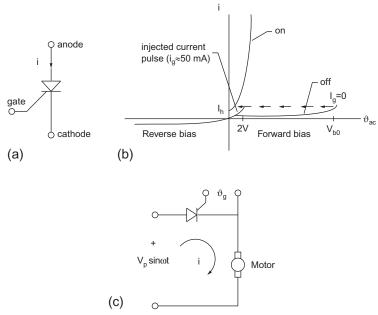

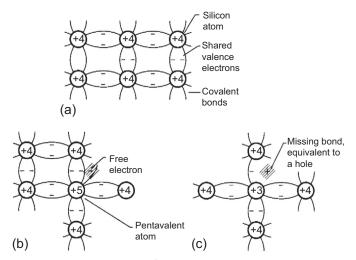

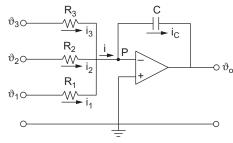

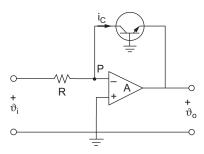

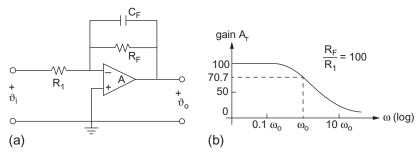

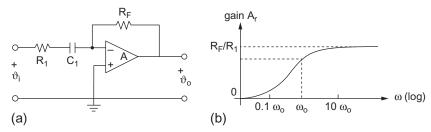

### 1.6.2 Superposition